Other Parts Discussed in Thread: ADC08DJ5200RF, , ADC12DJ4000RF, LMX1204, LMX2582

Dear, TI support team.

I have a question about the ADC08DJ5200RF or ADC12DJ5200RF.

One of our customers requires measurement equipment to sample between 50Gsps and 100Gsps.

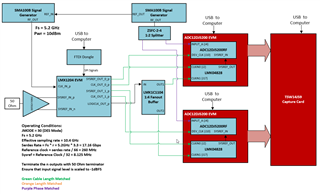

We are proposing to increase the sampling rate by connecting the fastest sampling A/D converters, ADC08DJ5200RF and ADC12DJ5200RF, in parallel.

However, neither we nor the customer have the know-how on time-interleaved connections,

so we would like to receive advice on how to synchronize the clock and avoid spurious errors such as jitter, offset, and gain errors.

The clock is generated from Vertex FPGA and uses JSED204B/C.

By the way, ADC12DJ4000RF is not listed in the overview, will it be discontinued?

https://www.ti.com/data-converters/adc-circuit/high-speed/overview.html

Best Regards,

HIroaki Yuyama