Hi team,

I plan to recommend ADS131M06 to my customer, could you help check these questions for me ?

1. Is the current life cycle of ADS131M06 recommended for new designs?

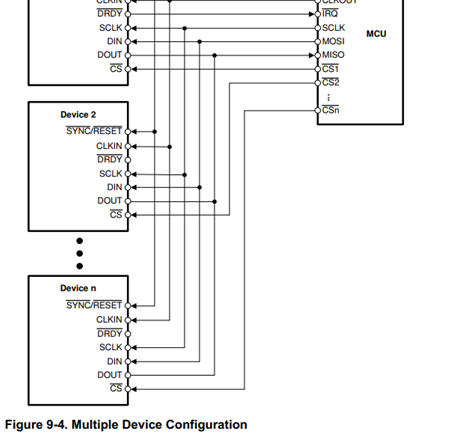

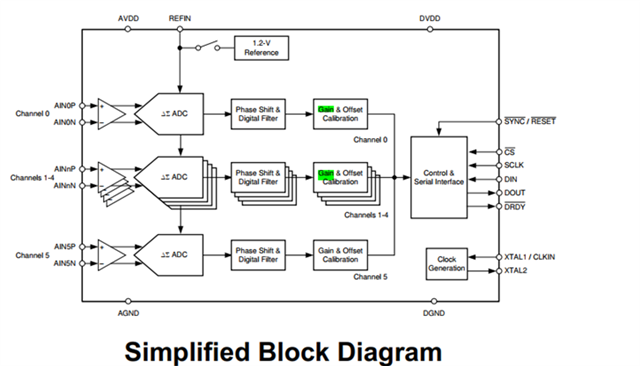

2. If you want to use three ADS131M06 chips for multi-channel sampling, how to achieve sampling synchronization of 3x6 = 18 channels? To achieve sampling synchronization, must all ADCs be based on the same clock source? How long does it take from SYNC/RESET to change to 1 until ADC starts sampling?

3. The Offset error parameter in the datasheet only provides two typical values. Does ±240 correspond to Continuous Conversion Mode? What is the maximum value of Offset error? If you change the Gain setting, will the Offset error also change?

4. Our application scenario is to input a current signal of 5mA – 300A. Can ADS131M06 complete data acquisition by adjusting the internal PGA without an external amplification circuit?

Thanks

Lillian