Part Number: TSW14J58EVM

Other Parts Discussed in Thread: ADC32RF55, TI-JESD204-IP

Tool/software:

I am conducting operation verification and learning with the above evaluation board, aiming at FPGA development to communicate with ADC32RF55.

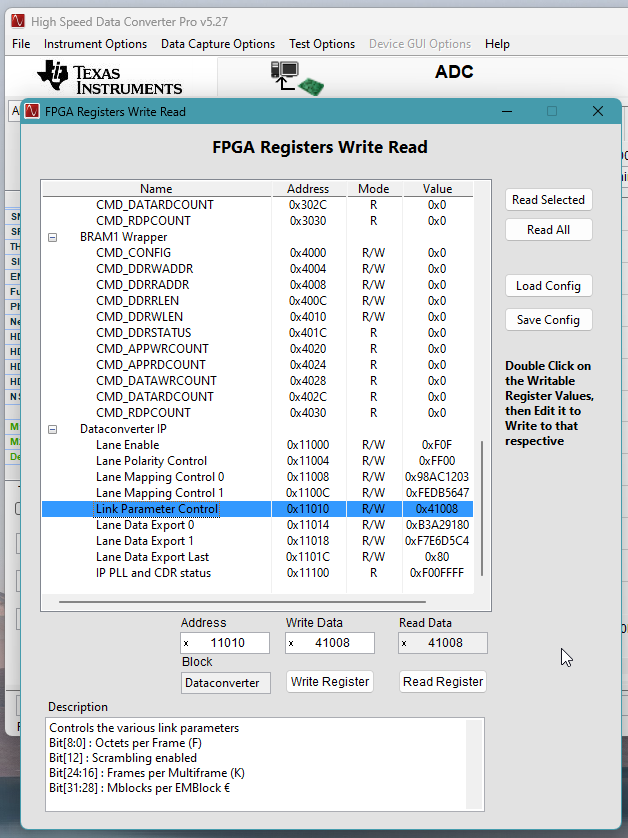

I was able to verify the operation according to the user guide, but I am looking for parameters related to the internal FPGA implementation and JESD204B for learning.

・Please let me know if any information about the FPGA for TSW14J58 written by HSDC Pro is available.

The information I am particularly interested in includes the K parameter and information about the delay of SYSREF.

If that is not available, please tell me the closest design. The important settings are LMFS=8224 / GTY / 14bit.

・Is it enough to prepare for writing to this evaluation board with JTAG by simply changing J29 to 2 to 3 > 1 to 2?

・Separately, sometimes the current value does not stabilize when operating as per the above product guide. Please let me know if there is a way to improve this.