Tool/software:

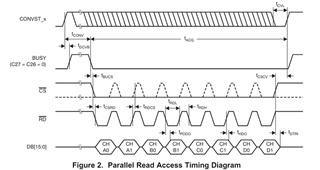

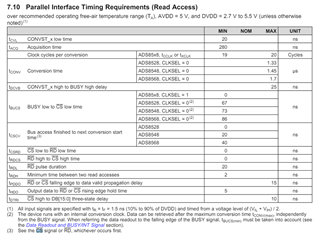

If we start pulsing /RD after the BUSY goes low, but /CS goes low a little later, after some /RD pulses have already been made (let's say 2). Will the data on the parallel bus for the 3rd /RD pulse (first with /CS low) be for A0 or for B0?