- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hi,

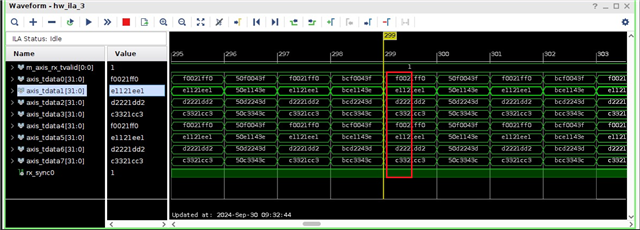

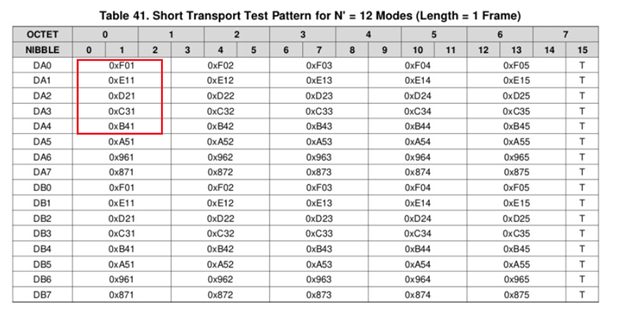

My customers are facing a problem when trying to use DJ3200 in a test mode. They tried to enter the test mode with N'=12, and the data they captured for each channel is as below figure1. The Pattern for DA0-DA3 is begin with F00/E11/D22/C33 instead of in the datasheet showed F01/E11/D21/C31. Are my customers correctly entering into the test mode? Are there anything else need to configure or any reasons that can cause the customers' scenario?

Pls give some suggestions on that, thanks.

BR,

Manu

Hello Manu,

Is the customer using the ADC12DJ3200 EVM or a custom board. It is important to note that LANE0 of the ADC will not necessarily route to LANE0 of the FPGA, so they must account for an lane mapping swaps in their FW to get correct data out.

Can you confirm how your customer is setting the ADC into test mode? And confirm that they are using the "Transport Layer Test Mode"

Additionally can you confirm if they are using TI JESD IP or Xilinx JESD IP? It is important to note that with Xilinx JESD IP you will have to unpack the data yourself, this to me seems like it could be the issue as they are close to matching the pattern but a little bit off.

Best,

Eric