Tool/software:

Hello,

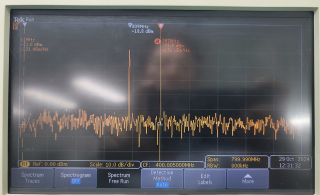

My customer is testing the signal output of the DAC39RF10 device alone on a board they designed.

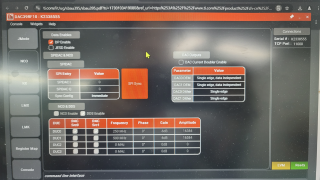

They used the settings below, which were confirmed to be output normally in standalone mode on DAC39RF10EVM.

DAC39RF10.read(0x02E8) # = 0x00 DAC39RF10.write(0x0000,0x80) time.sleep(0.1) DAC39RF10.write(0x0101,0x04) DAC39RF10.write(0x0102,0x04) DAC39RF10.write(0x0103,0x13) DAC39RF10.write(0x0108,0x10) DAC39RF10.write(0x0109,0x21) DAC39RF10.write(0x010A,0x01) DAC39RF10.write(0x010B,0x01) DAC39RF10.write(0x0103,0x13) DAC39RF10.write(0x0103,0x11) DAC39RF10.write(0x01C2,0x01) DAC39RF10.write(0x02E1,0x07) DAC39RF10.write(0x02E3,0x01) DAC39RF10.write(0x02E4,0x11) DAC39RF10.write(0x02E8,0x00) DAC39RF10.write(0x0723,0x1F) DAC39RF10.write(0x0724,0x0F) DAC39RF10.write(0x0725,0x1F) DAC39RF10.write(0x0726,0x0F) DAC39RF10.write(0x072E,0x14) DAC39RF10.write(0x072F,0x14) DAC39RF10.write(0x0739,0x14) DAC39RF10.write(0x0100,0x01) DAC39RF10.write(0x02E0,0x01) DAC39RF10.write(0x02E0,0x00) DAC39RF10.write(0x0100,0x00) DAC39RF10.write(0x02F0,0x01) DAC39RF10.write(0x02F2,0x7F) DAC39RF10.write(0x02F1,0xFF) DAC39RF10.write(0x02F0,0x00) DAC39RF10.write(0x0300,0x01) DAC39RF10.read(0x02E0) # = 0x00 DAC39RF10.write(0x02E0,0x00) DAC39RF10.write(0x02E4,0x01) DAC39RF10.read(0x02E0) # = 0x00 DAC39RF10.write(0x02E0,0x00) DAC39RF10.write(0x02E4,0x21) DAC39RF10.read(0x02E0) # = 0x00 DAC39RF10.write(0x0327,0x10) DAC39RF10.write(0x0326,0x46) DAC39RF10.write(0x0325,0xAA) DAC39RF10.write(0x0324,0xAA) DAC39RF10.write(0x0323,0xAA) DAC39RF10.write(0x0322,0xAA) DAC39RF10.write(0x0321,0xAA) DAC39RF10.write(0x0320,0xAA) DAC39RF10.write(0x0304,0x00) DAC39RF10.write(0x0304,0x01) DAC39RF10.read(0x02E0) # = 0x00 DAC39RF10.write(0x032F,0x20) DAC39RF10.write(0x032E,0x8D) DAC39RF10.write(0x032D,0x55) DAC39RF10.write(0x032C,0x55) DAC39RF10.write(0x032B,0x55) DAC39RF10.write(0x032A,0x55) DAC39RF10.write(0x0329,0x55) DAC39RF10.write(0x0328,0x55) DAC39RF10.write(0x0304,0x00) DAC39RF10.write(0x0304,0x01) DAC39RF10.write(0x02E0,0x01)

Q1. Please advise on the cause of this issue and how to resolve it.

Q2. Is SYSREF clock required even when checking output on device with standalone?

Q3. Please review the customer design below to see if there are any problems.

DAC39RF10ACK-1.pdfDAC39RF10ACK-2.pdf

Thank you.

JH