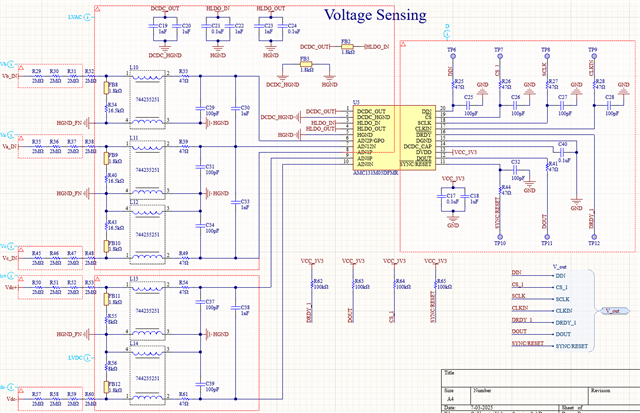

Other Parts Discussed in Thread: ADS131M04, , SN74LVC1G17, AMC3336, AMC1336, AMC0386, SN6501, UCC33020, ADS1204, ISO6761

Tool/software:

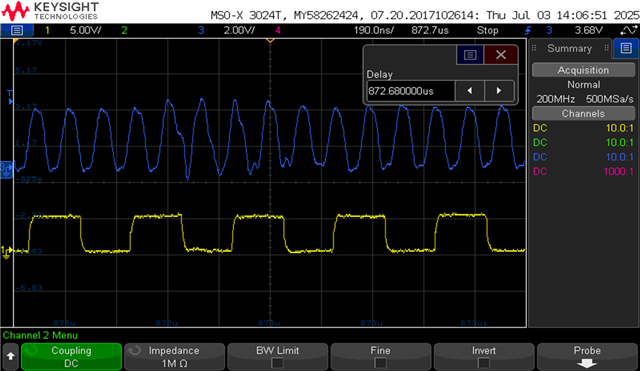

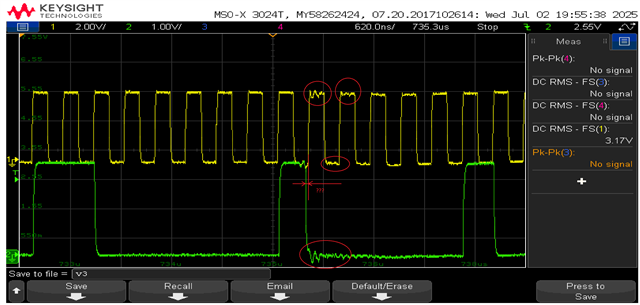

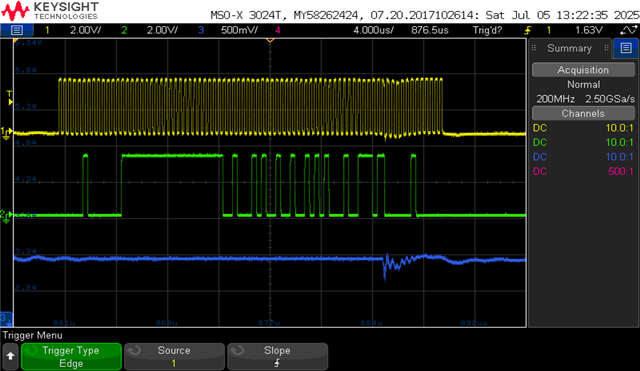

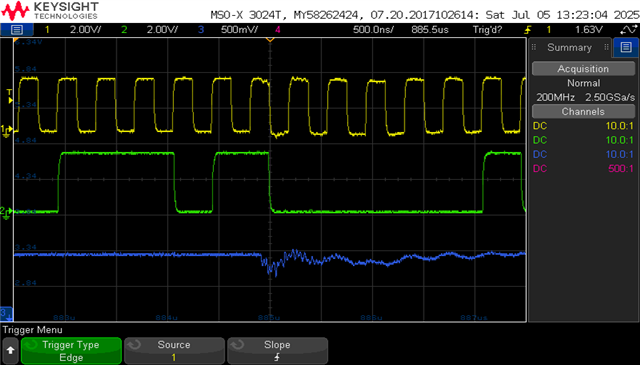

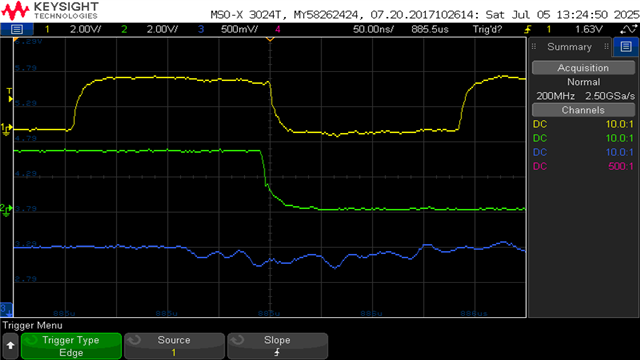

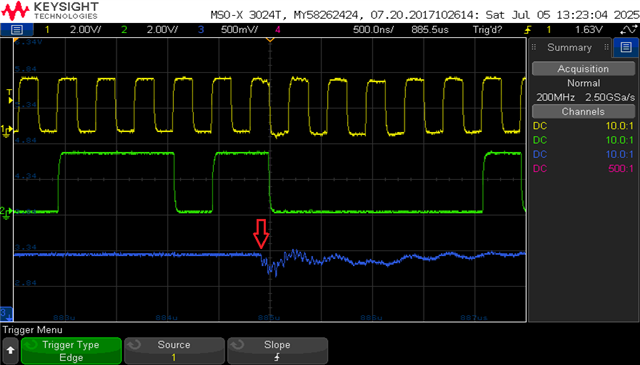

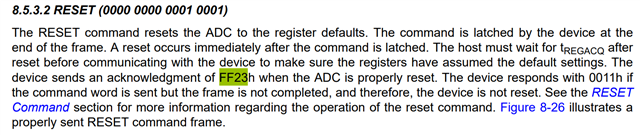

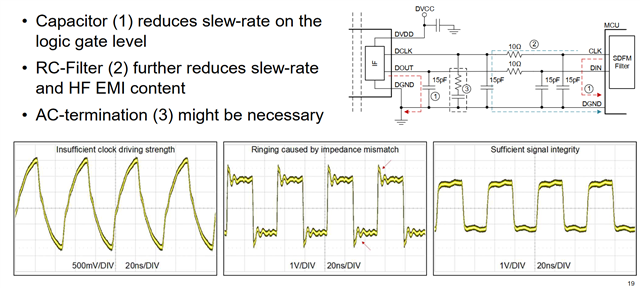

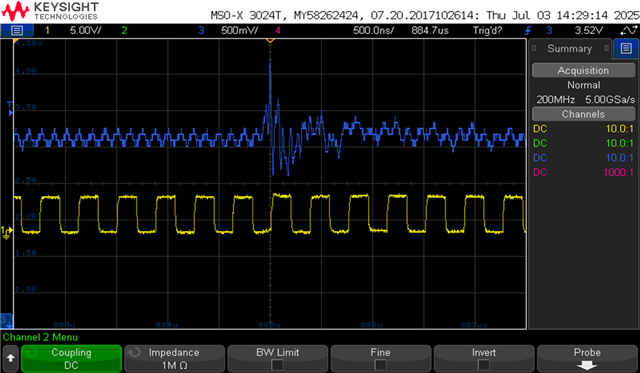

Hi im using AMC131M03 and ADS131M04, im having an issue in crc, in what are the ways the crc mismatch error can come, input crc im not using, im using only output crc received from devices and im using ccitt crc polynomial. my spi clk is 5.3mhz, mode 16bit , clock in 8mhz and osr is 64ksps. so in my case crc is not matching when enabling the switching (PWM) for the converter. during that time my crc is half of the time not matching what could be the reason for crc mismatch. im reading the data every 50us, with single spi bus of two devices, i dont know in what are the ways that crc mismatch can happen. after finishing the parameter configuration initally 1- or 2-time crc is not matching after that it is perfectly fine for both the devices. when started switching it becomes crc error and my switching is based on the values reading from spi .it is any timing issue or clock issue or any noise affecting.

if data is not ready im reading the data during that time the crc mismatch can happen or not?. and im not usng drdy pin due to interuppt handling, so every 50us im reading the data. can anyone suggest or helpme to findout why crc mismatch is happening. why it is happening in during first time reading after parameters configuration also.

regards,

srinath