Other Parts Discussed in Thread: TI-JESD204-IP, ADC12QJ1600

Tool/software:

Hello,

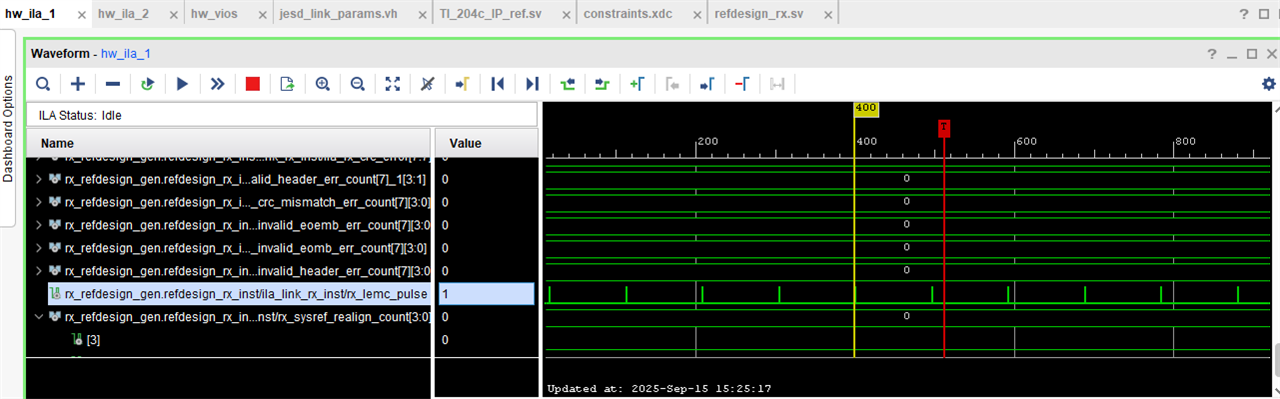

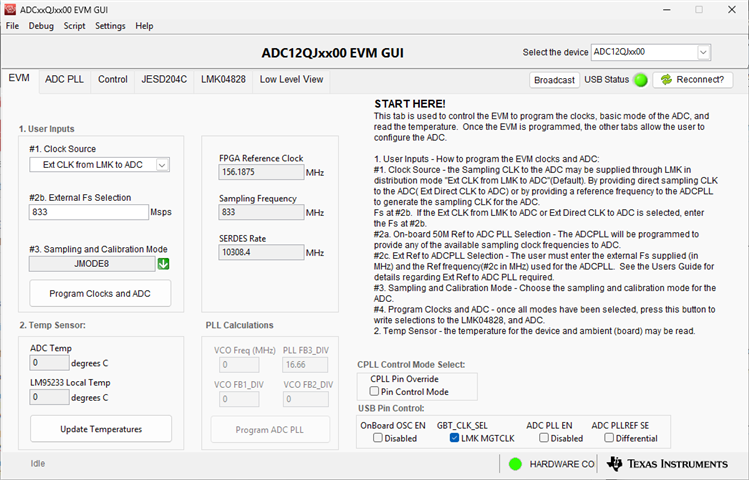

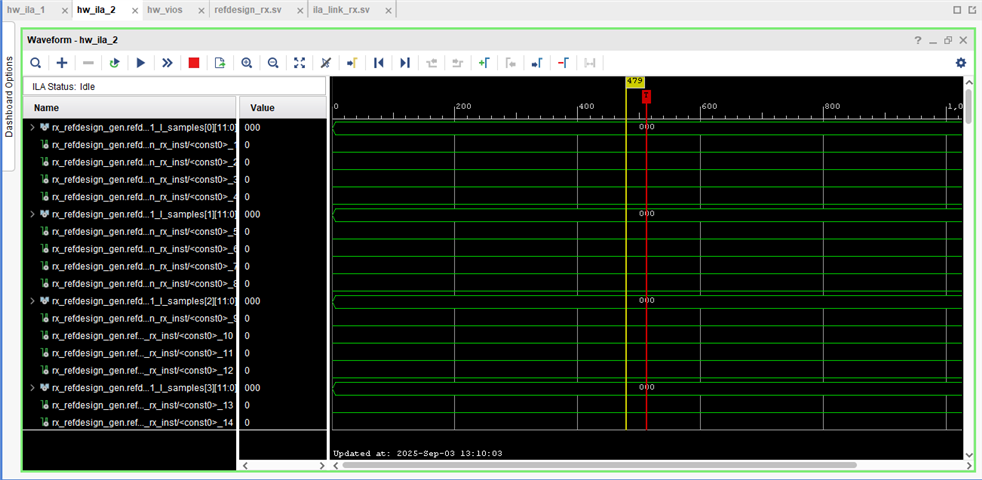

I am working with the ADC12QJ1600 EVM and the TI-JESD204-IP and have questions on how to configure the ADC12QJ1600 EVM GUI. I have set up the JESD IP to be 64b/66b, receiving with 4 lanes and believe with an external clock connected to LMK CLK, I can pass patterns to my FPGA that should be viewable on the ILA.

I believe my constraints are correct (FPGA_GBTCLK0_FMC from ADC mapped to refclk in the IP, FPGA_SYSREF_FMC to sysref and FPGA_CLK_FMC to sys_clk, and the data lanes).

I am using JMODE8 with 833MHz external clock to start with, as this results in a lane rate and FPGA clk similar to what is default in the JESD-IP as I just wanted to see any signal come through, and changed the JTEST register to attempt ramp and transport test modes but could not see any results in the FPGA ILA.

I would like if someone could run me through the settings I need to change to make the ADC compatible with the IP, to make signals visible in the ILA, so I can confirm that the ADC, and hence the JESD IP are set up correctly.

Thank you.