Hi,

I connected ADS54RF63EVM to Virtex 6 FPGA board. I am capturing the adc_diff_data into an IDDR, which is clocked by dry_clk. But, my data is observed on ChipScope ( Xilinx tool to see internal signals ) and is found to change NOT with respect to the dry_clock!

1. data coming to the flip flop is not synchronous with the clock

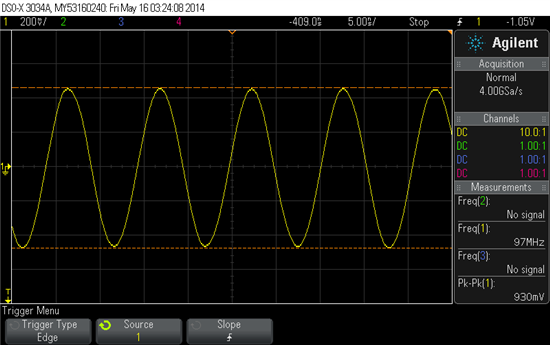

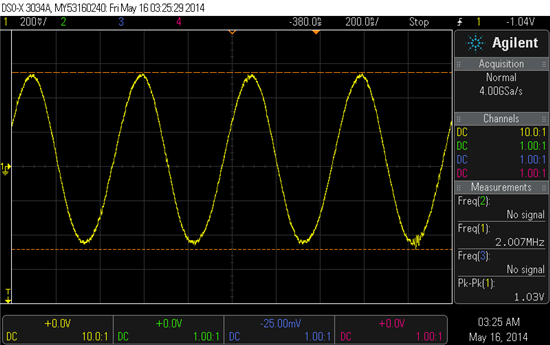

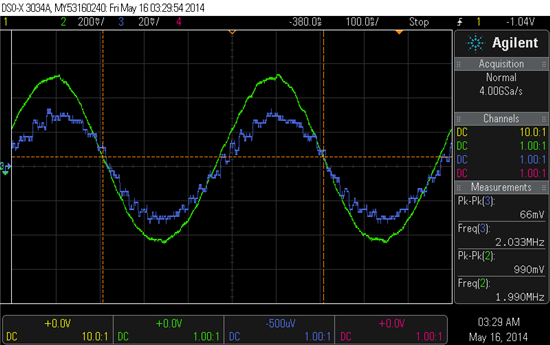

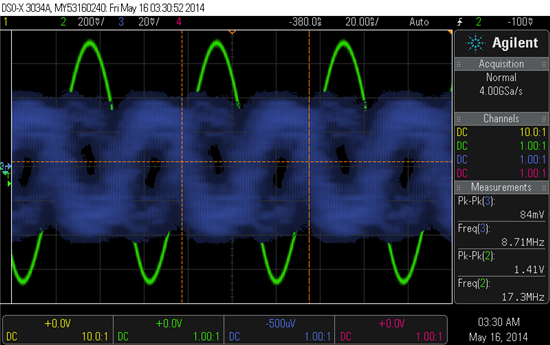

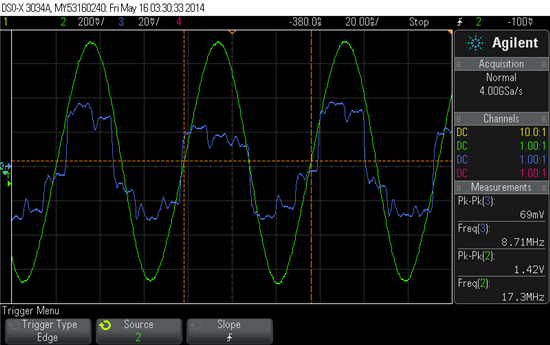

2. I used the dry_clk inside the fpga, and sent it out via the sma_out of the FPGA board. It does not look like a sinusoid! Infact, it's shape changes with the frequency! Sometimes, it's close to a sine, otherwise it's something else !

I have been trying on this ADC board for a long time now, and I tried different ways to debug the issue, such as combining ADC-FPGA-DAC, using flip flops to sample, using IDDR to simple ( the simplest way ). No issue has helped me to obtain a faithful representation of the ADC working!

At this point, I seriously doubt if the ADS54RF63EVM board with me is in working condition or not! Using this board is extremely crucial for my work, and I would very much appreciate any help in this regard.

Thanks a lot in advance,

Basil.