Hello,

In the datasheet P.40 of ADS7954, there the discriptuon about restrinction on source impedance.

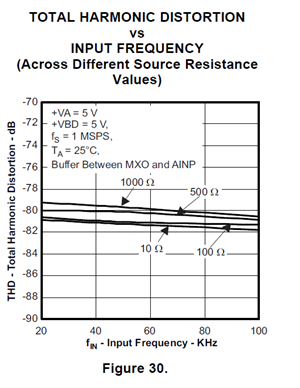

Could you please let me know maximum source impedance with buffer between the MXO and AINP pins ?

Our customer added a common ADC driver buffer between the MXO and AINP pins with 1Mohms source impedance.

Then they faced bad linearity and THD.

Best Regards,

Ryuji Asaka