Hi,

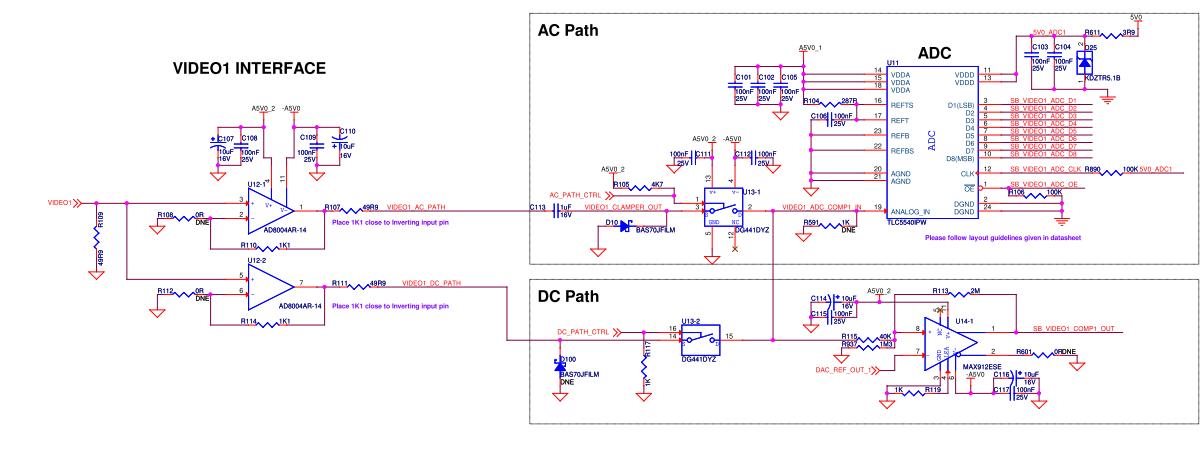

We are using the TLC5540 chip on our board interfaced to a Virtex6 FPGA (Schematic attached).

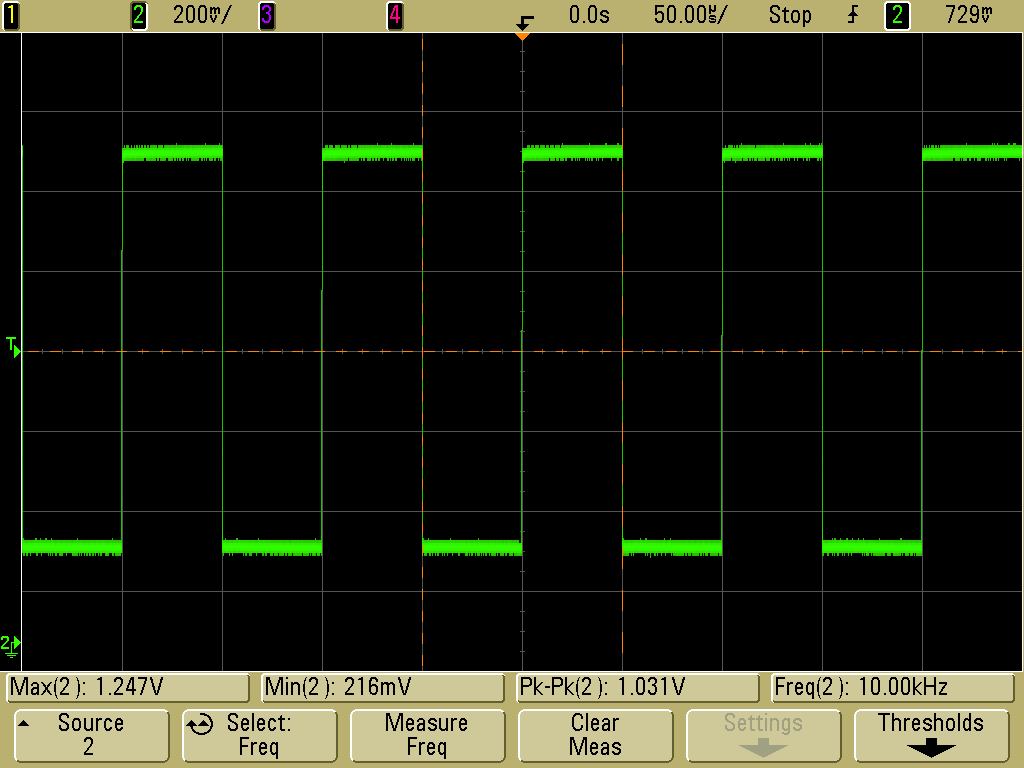

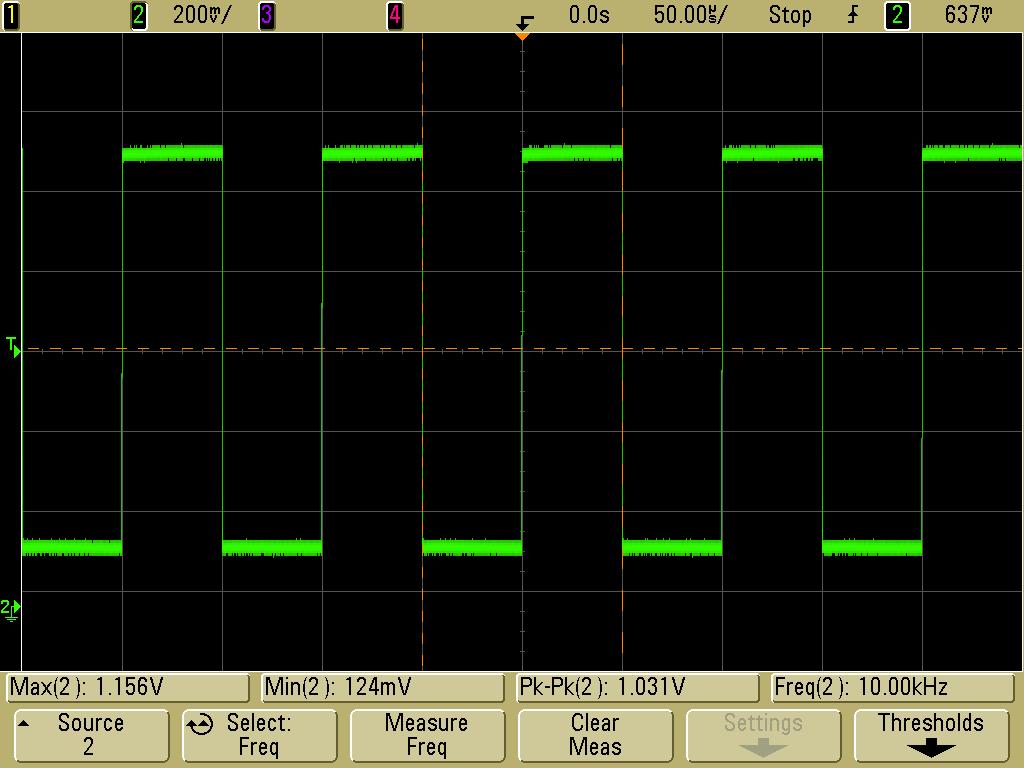

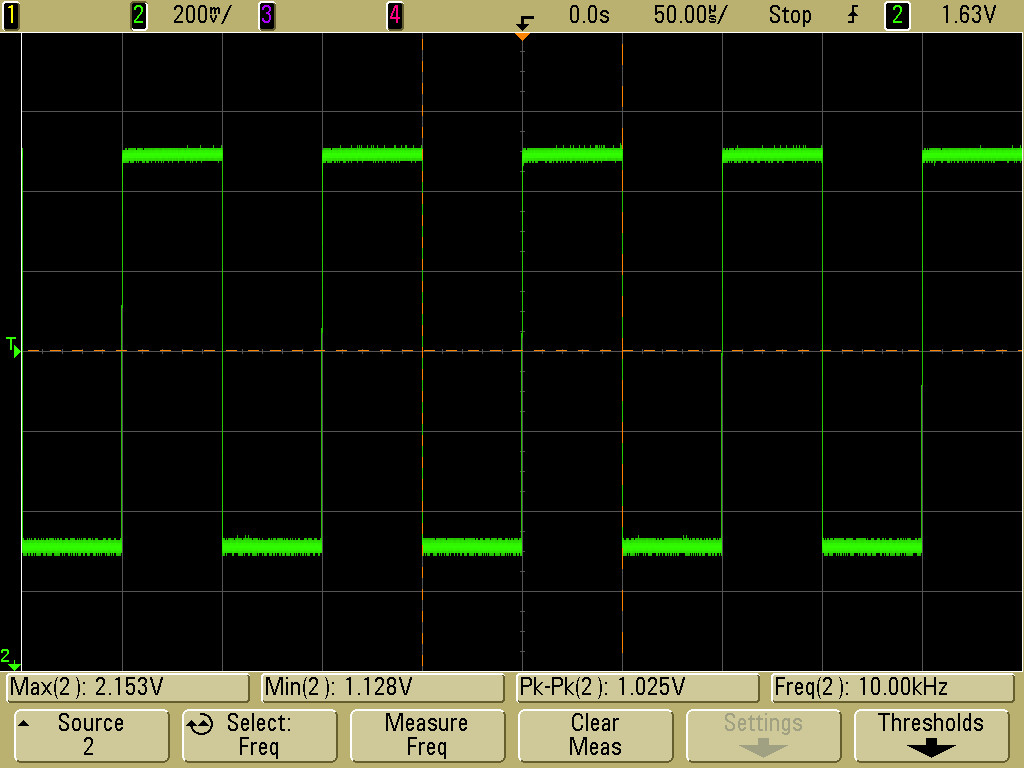

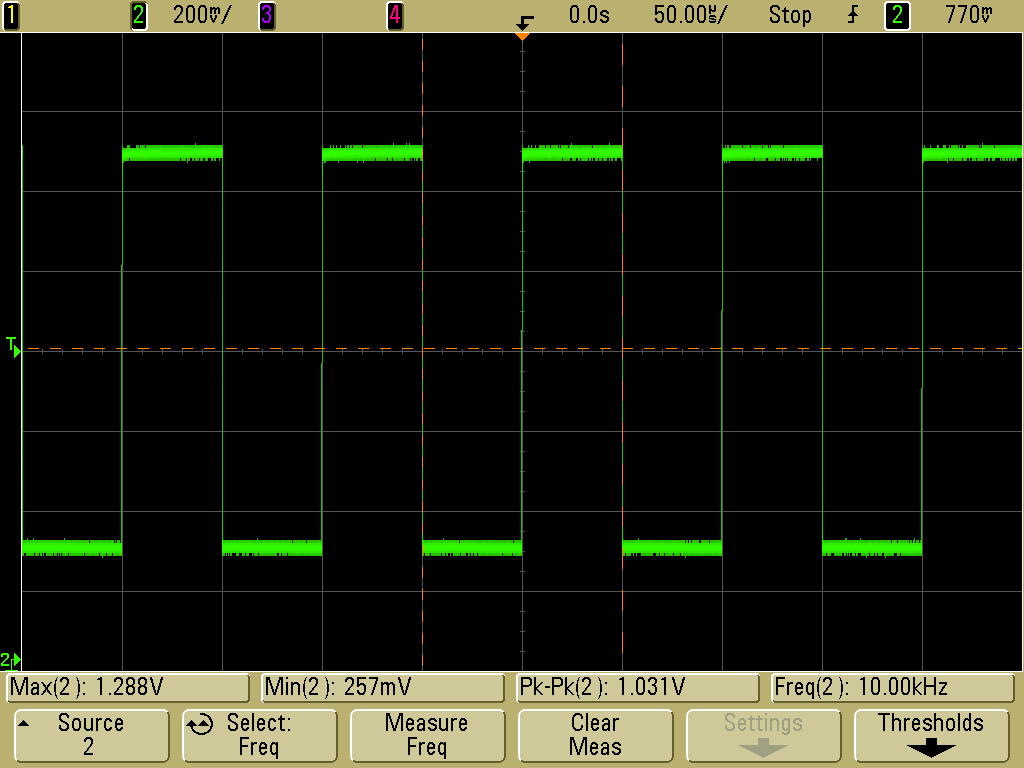

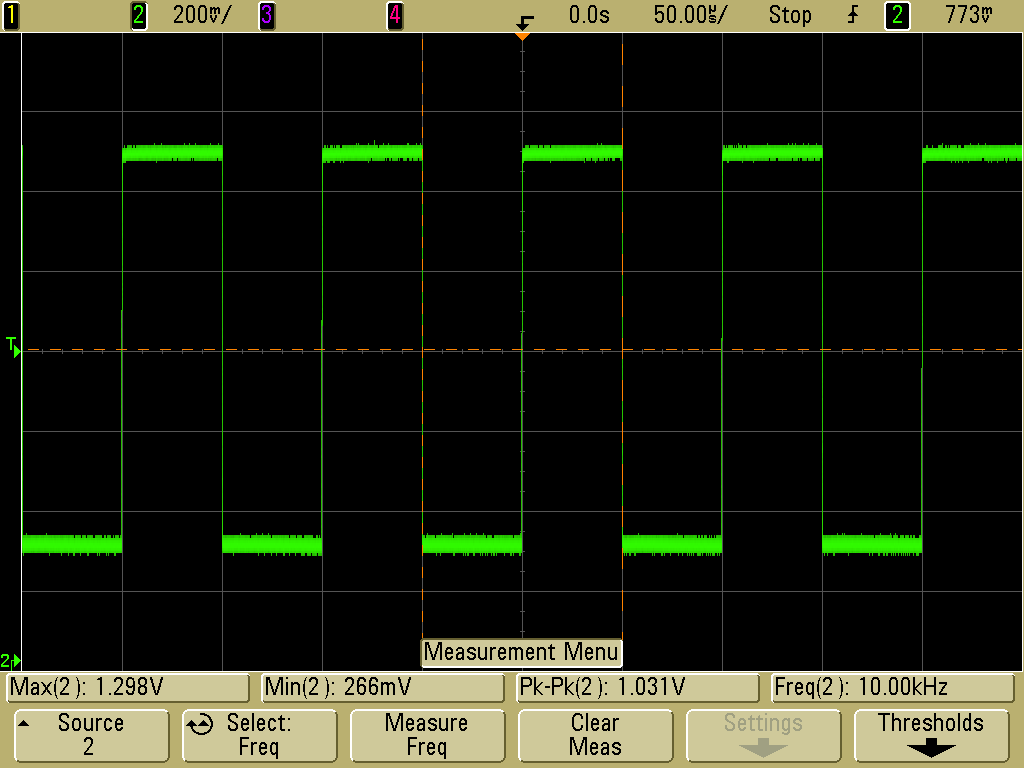

We are using it for sampling an input video signal fed from a Function Generator (with 50ohm output impedance) at 40MSPS. The circuit was working fine for over a week. Since yesterday, when we are feeding an input sinusoidal signal swinging between 0 to 3.2V at 10kHz through the AC path or DC path of the design, we are observing a DC shift of approximately 1.5V on the input signal at the ADC input. This, in turn, is causing errors in the data captured by the ADC.

To find the root cause of this problem, we tried isolating the analog input using the RF switch in between. We found that with no input signal applied to the ADC, a 1.5V DC voltage was still coming at the ADC input.

Since we had a comparator (MAX912) also in the path, we suspected the comparator to introduce this DC level. So we isolated the comparator input from the circuit by removing the series resistor R115.Still, a 1.5V dc was coming at the ADC input without any analog signal applied.

We had a provision to enable/disable the sampling clock to the ADC. When we disabled the 40MHz sampling clock to the ADC, we found that the DC level came down to zero. When the clock was enabled again, 1.5V dc started coming again at the ADC input.

Why is this DC level shift happening at the ADC input? What can I do to overcome this dc level shift from affecting the ADC data capture as well as other circuits?

Regards,

Avinash