Hello,

I am using theTLV2556 in a new product. I'm seeing some crosstalk across channels and realized that I'm violating the chip’s analog voltage input range by going below -0.3 and above Vcc + 0.3. I have design choices so I have a couple questions:

- Exceeding VREF. The datasheet recommends that the analog voltage not exceed VREF. If I exceed VREF but do not exceed VCC I know that the converter will output maximum count but is there any risk of crosstalk?

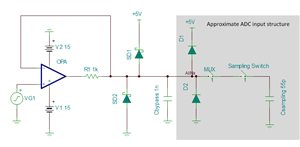

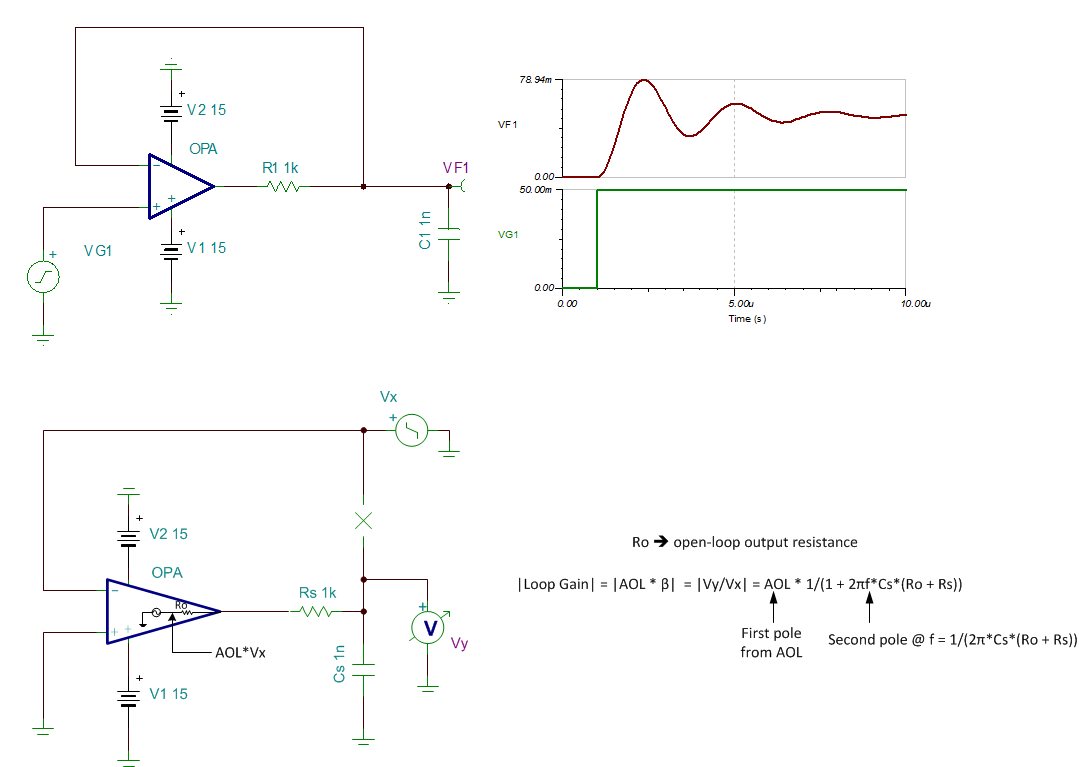

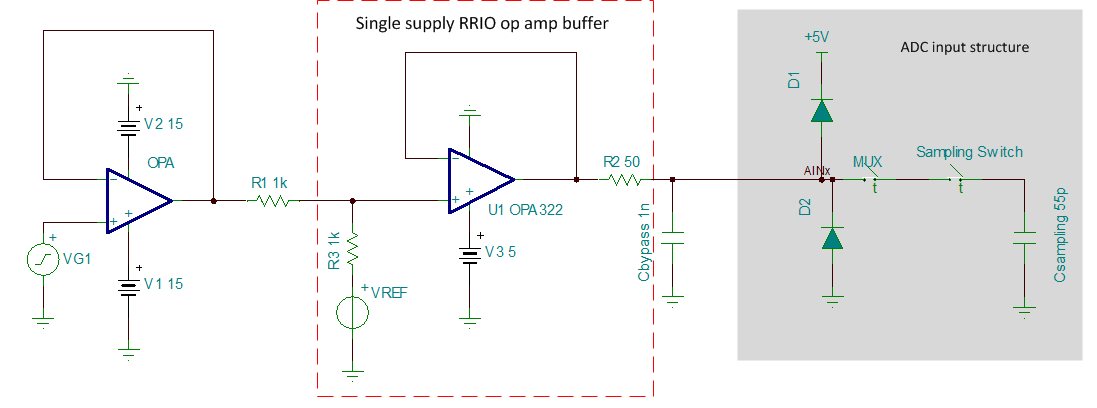

- I’m using opamps powered by +/-15V that present voltage to the TLV2556. We are using series resistance and clamp diodes to VCC and ground. I can keep the analog input voltage to the converter within limits by using better performing diodes and increasing the series resistance to 1k ohm. Does this create a potential problem? I noticed that the Analog input MUX impedance can be as high as 600 ohms but I’m not sure what this is.

Thank you for your help.

Russell