I'm working on a ADS5281 EVM interfacing with Xilinx Virtex5.

The main sampling rate was 50 MHz given from FPGA.

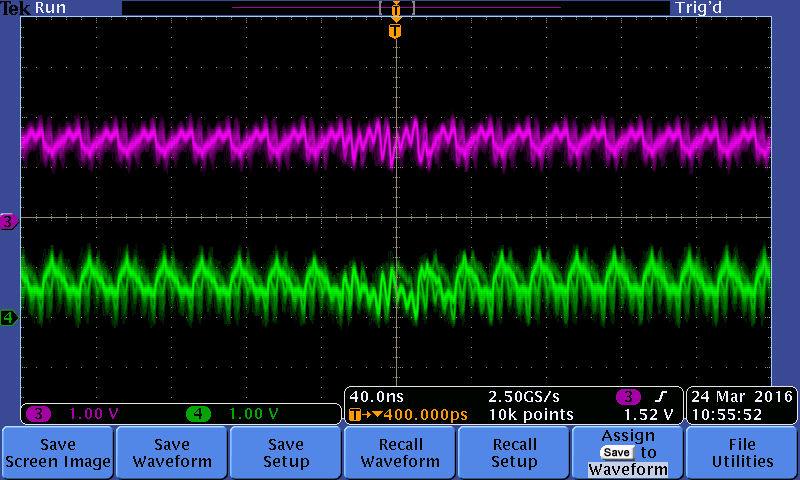

I'm wondering why I could see the output ADC signal (as following figure) with reset command via SPI software and no input analog signal.

Is it right? What kind of ADC output signal can be extected without any input analog signal?

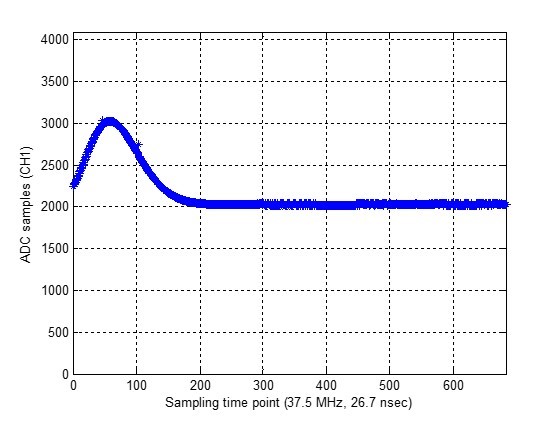

I think this background signal affects the ADC output signal when I feed an anlog gaussian signal to ADS EVM.

In FPGA, I got two correct frame and bit clocks, but the deserialized data of each channel has only two or three distinct adc values (like 0, 2046, 4095).

If I use 'Deskew' or 'Sync' test pattern, I could see clear Deskew or Sync ADC outputs on osciloscope.

But if I gave a command, "reset" by SPI software to feed an analog input into ADS EVM, I can't get a correct signal on oscilloscope and fpga chipscope.

Please give me some comments on how to start ADS EVM correctly with an analog signal or if there is some steps I missed.

This is the procedure how I start the ADS EVM:

1. power on ADS 5281 EVM

2. connect the usb of EVM to my PC (windows7)

3. perform "reset" command by SPI software.

4. check the output adc signal on osciloscope

5. give a command of "Sync" test pattern on SPI software

6. check the output adc signal on osciloscope

7. perform "reset" command by SPI software.

8. feed an gaussian analog signal to ADS EVM

9. check the output adc signal on osciloscope

Thanks,

Soo Mee.