Other Parts Discussed in Thread: LMP90099,

Hi.

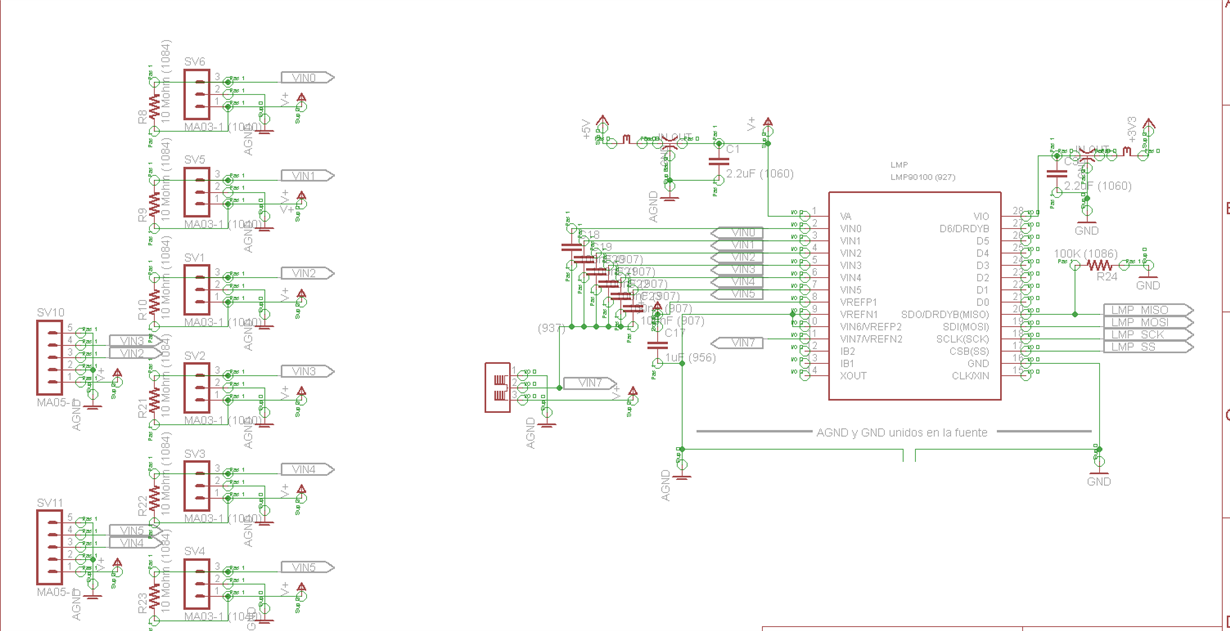

This device features 4-DIFF / 7-SE Inputs (LMP90100/LMP90099). However we saw through data sheet that there would be no drawbacks about using more than four differential channels in our application if we arranged our circuits in order to share one or more common inputs. And that is what we did in the following way:

CH0 = VIN0-VIN7

CH1 = VIN1-VIN7

CH2 = VIN2-VIN7

CH3 = VIN3-VIN7

CH4 = VIN4-VIN7

CH5 = VIN5-VIN7

(VIN6 not used, connected to gnd).

Each sensor is a force load cell made of a double strain gage, configured as a half bridge. We conect them to each of six measuring inputs and use a seventh strain gage on board as a reference. (*) see below more configuration parameters.

Could not upload circuit. Linked image here: drive.google.com/.../view

VREF_SEL = 0 for every channel. This means VREFP1 and VREFN1, which are being connected to sensors power and gnd respectively.

This would allow us to obtain six independent measurements from six half-bridge load cells. Where VIN0 to VIN5 are connected to mid point of those half bridges, and VIN7 is connected to a common reference half bridge. This meets all requirements of a coarse balanced wheatstone bridge in order to work as a substitution/comparison-measurement method.

We have used this configuration for years. And this year we started to employ LMP as a greatly promising sensor AFE, with very convenient advantages respect to its competitors. But unfortunately :( obtained two issues that must be solved:

a) A noticeable cross-talk among channels. That means when a channel goes to rails because of absence of the corresponding sensor (a weak pull up 10Mohm resistor is always present in our circuit), that event modifies values obtained in other channels that do have a sensor plugged in. Besides, when all sensors are present you can see aprox. a 5% cross-sensibility from any channel to others. Today this is patched by software app, but must be improved.

b) Some "noisy" parts. We have manufactured and sold more than one thousand equipments with LMP90100 and noted at QC tests that some LMP devices, about 15% show themselves much more noisy. For those boards the effective number of bits observed falls to 12, when 17 stable bits are expected and used in the 85% of remaining boards. Replacing those apparently-noisy LMP90100 (by "noise-free" devices) through reworking the same pcb, solves this issue. As an experiment, if we lower sample rate from 107 sps to 13 sps or below, noise performance improves greatly and allows 16 or 17 stable bits measures, yet on apparently-noisy devices. I know that low ODRs enhance low pass digital filtering, but why only a portion of ICs are unduly affected?

I think we are missing something important about this device and hope you can provide some help or orientation as we are planning next production.

By the way I hope TI can consider re-writing this great-device's datasheet in order to make it less confusing or less ambiguous about ODR, digital filtering, and adding transparency to background calibration internal operation.

Thanks in advance!

(*)

PWRCN always in active mode

CLK_SEL default, internal clock.

CH_SCAN: Sacan mode 2, First CH0, Last CH5.

CH0 to CH5 CHx_INPUTCN & CHx_CONFIG

Bournout disabled

VREF_SEL = 0, VREFP1 and VREN1

CH0 = VIN0-VIN7

CH1 = VIN1-VIN7

CH2 = VIN2-VIN7

CH3 = VIN3-VIN7

CH4 = VIN4-VIN7

CH5 = VIN5-VIN7

(VIN6 not used, connected to gnd).

ODR_SEL = 0x6, 107 sps

GAIN_SEL = 0x6, 64 with FGA on

BUF_EN = 0.

BGCALCN. BGCALN = 0, off.