First time using the part and have SPI questions. Using a Microchip controller and set CKE and CPOL to 0 - SCLK is running at 500khz.

The chip responds to 8 bit commands - writeSPI4(0x08); //start conversions - ~DRDY active *see the pin going low

writeSPI4(0x06); // ~DRDY inactive *see all pins going to reset state

I have a BEAGLE SPI analyzer see activity on MISO on 8 bit above transfer.....didn't expect it.

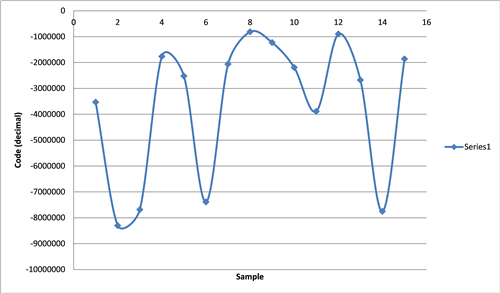

Also, set up read register protocol as directed but data read is garbage. Am I missing a relationship between setting a function using a pin or SPI command?

Thanks