Part Number: ADS1015EVM

Debugging some strangeness in conversions, I decided to implement the ADS1015 ALERT/RDY line for an interrupt-driven method of reading the results register in both auto and manual conversion mode.

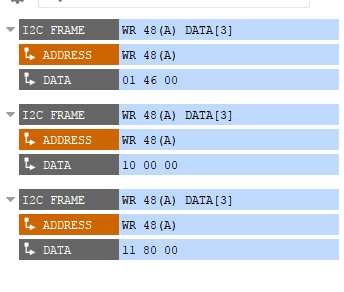

I have set the config register, bits 0 to 4, to 0x03, per the data sheet. This is expected to provide an active low signal when a conversion is complete.

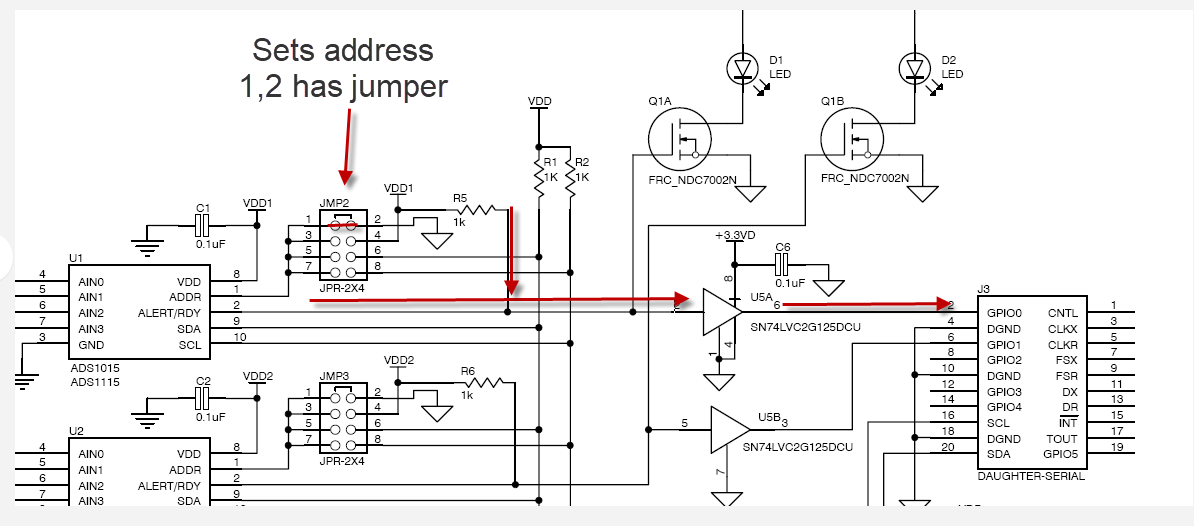

I am using the ADS1015EVM (Rev C) board in my test hardware.

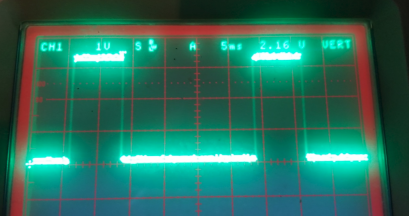

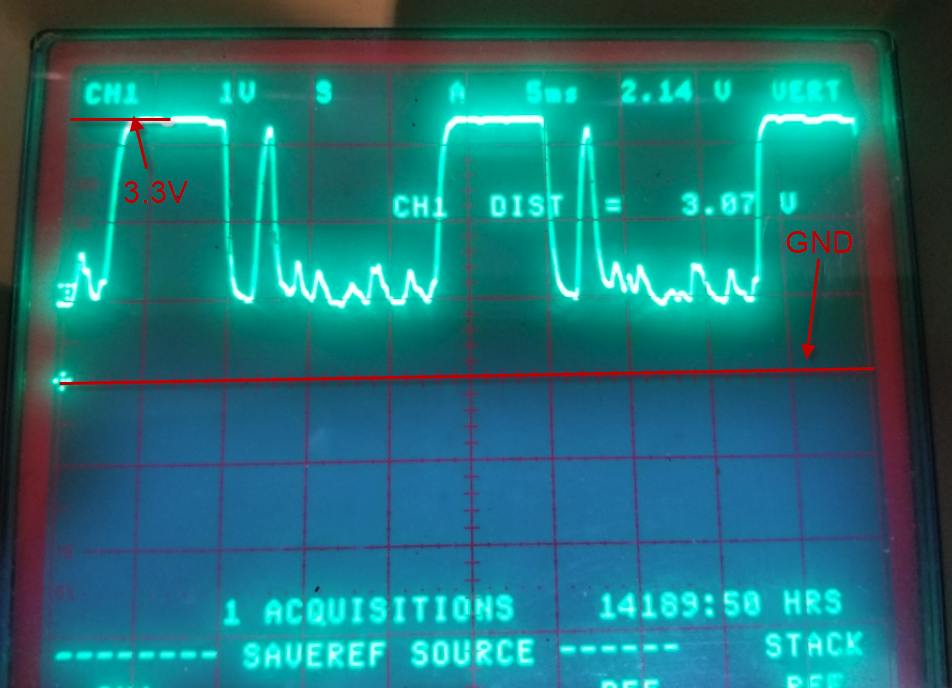

Examining this line on a scope caused some concern.

This happens with both ADS1015's and on both READY/ALERT lines.

I have two ADS1015EVM boards, so swapped in another one. Same result.

I replaced one of the ADS1015 ADC's. No change.

I removed Q1A/B. No change.

This is quite perplexing. I see the same ragged crappy signal on both sides of the non-inverting buffer, U5.

Here's a snip of my ADS1015EVM schematic:

This is rather late in the game for our development commitment to this device. So would be good to know, ASAP, if we can use READY/ALERT on this chip. At the moment, this seems unlikely.