Other Parts Discussed in Thread: ADC32RF45, ADS54J42, LMX2582

I have a customer using the ADC32RF45EVM in his application. He explains his issue below:

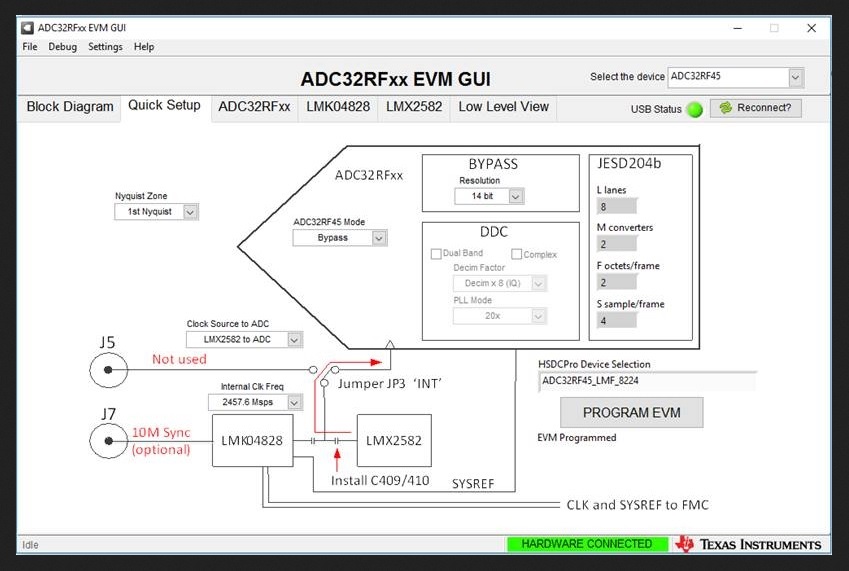

I am using the Xilinx KCU105 with the ADC32RF45EVM. I am following the instructions in the "HSDC Pro with Xilinx KCU105.pdf" document. But when it gets to the board setup example (Section 7.3) it only has an example using an external clock. I do not have an external clock available. I have tried to configure it for an internal clock, but I continue to get errors. My board has C409/410 installed, not C431/432.

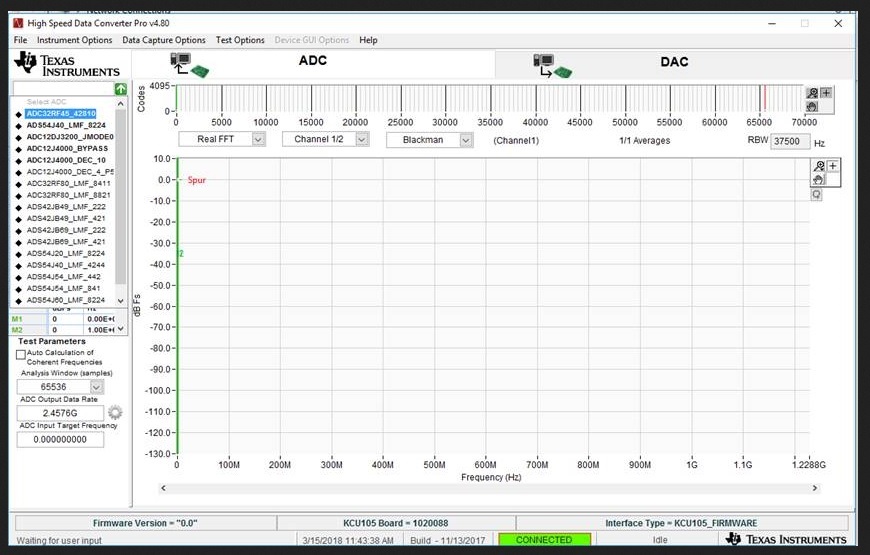

I have tried using various configuration files you provide, but none seem to work. When I put it in time domain and hit "Capture", I get "Configure ADC CMD_EXEC_ERROR when control command fails". If I click "OK" and try again, I get "Read DDR to file TIMED_OUT_ERROR Time Out error"

Do you know what might be happening here? Is this just a software issue? I thought that it might, but the inability to reconfigure the clock made me think that this might be related to something else.

Please let me know if you have seen this issue before and if you might have a solution.

Thanks for your help with this!

Richard Elmquist