Other Parts Discussed in Thread: TCA9548A, TCA6424A, , TPS2024, ADS1015, ADS1115, ADS7823, ADS7142, ADS7924

Hi team,

The customer has connected three devices on I2C, but TLA2024 was I2C communication failed, The other devices, which are TCA6424A and TCA9548A, don't have communication failed.

I2C configuration is below.

Sleve Addr : 48h (ADDR Pin : GND)

Vdd : 3.3V

I2C BUS Pull-up Resistor : 2.4K Ohm

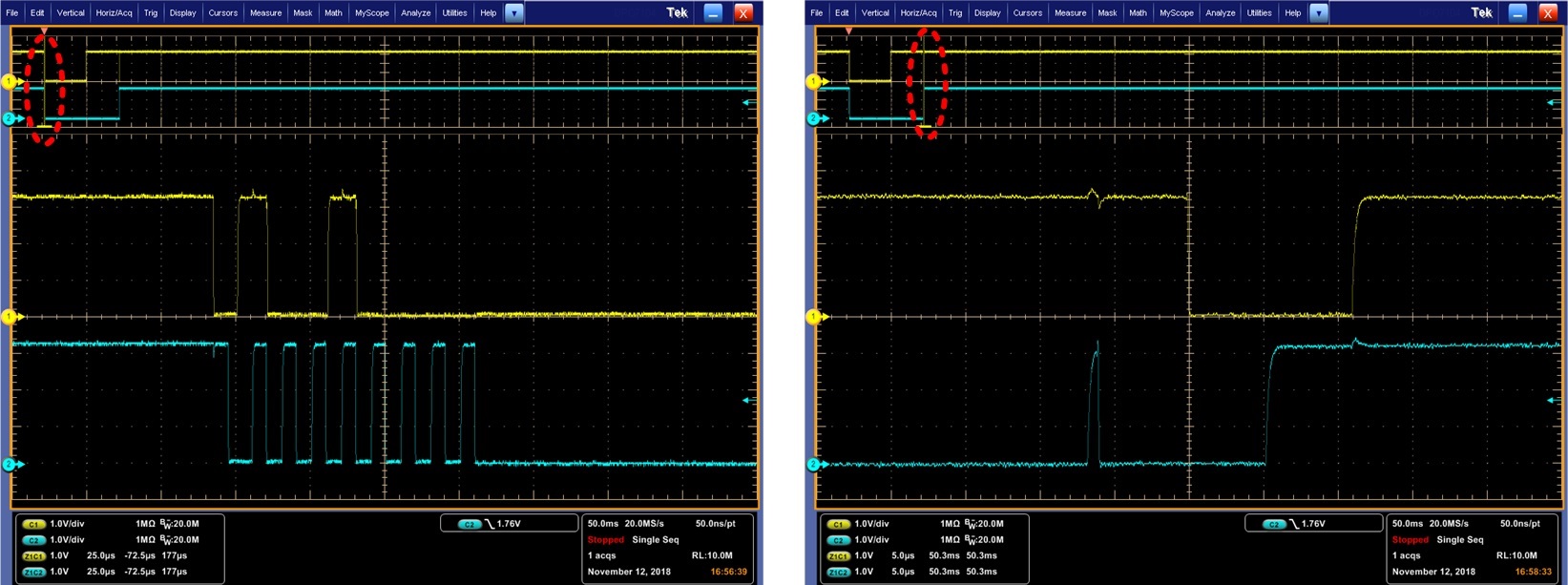

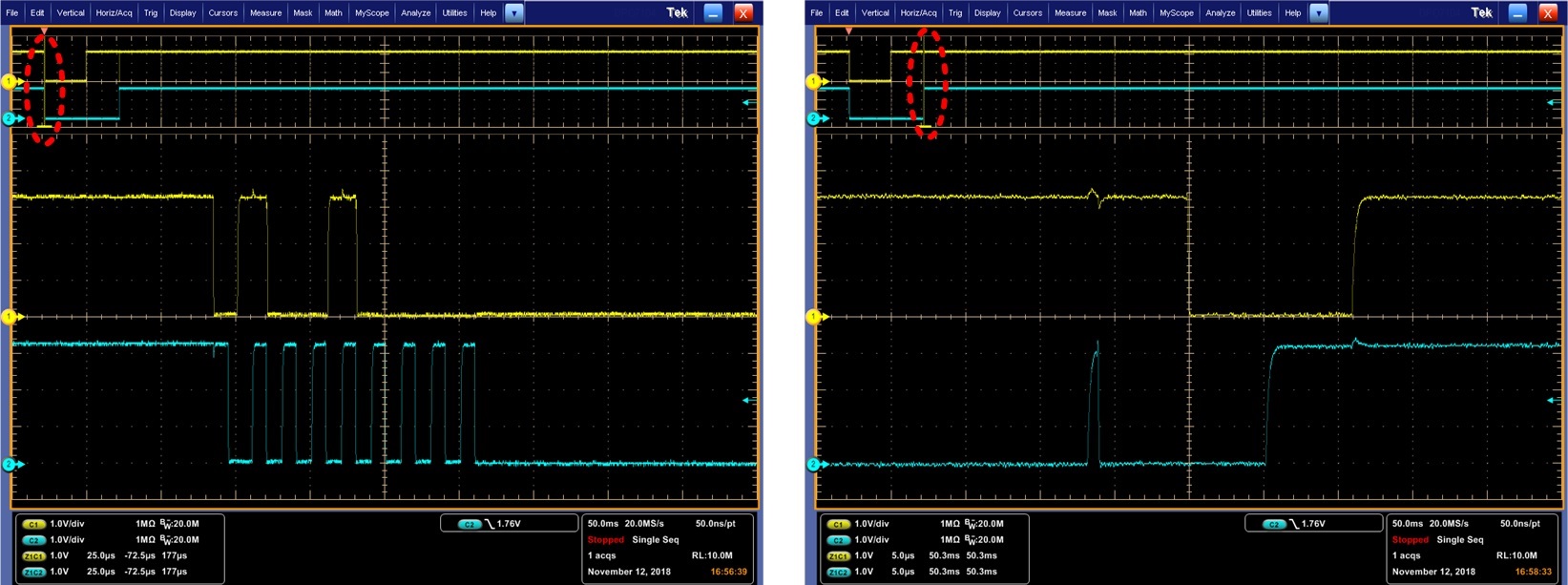

I attached the waveform, please check this.

I have some questions.

1. The 9th clock looks too slow.

Is cause of the I2C communication error TLA2024 time out?

2. Do you have anything other than this?

3. How to fixed this issue?

4. If TLA2024 is difficult to fix this issue, is there any other candidate device?

Regard,

Ogasawara

Hi team,

The customer has connected three devices on I2C, but TPS2024 was I2C communication failed, The other devices, which are TCA6424A and TCA9548A, don't have communication failed.

I2C configuration is below.

Sleve Addr : 48h (ADDR Pin : GND)

Vdd : 3.3V

I2C BUS Pull-up Resistor : 2.4K Ohm

I attached the waveform, please check this.

I have some questions.

1. I2C ACK response looks too slow.

Is this cause of I2C communication failure?

2. Can you think of anything other than this?

3. How to fixed this issue?

4. If this problem is in TPS2024, is there any other device?