Other Parts Discussed in Thread: TMS320F28335, , THS1206

Tool/software: Code Composer Studio

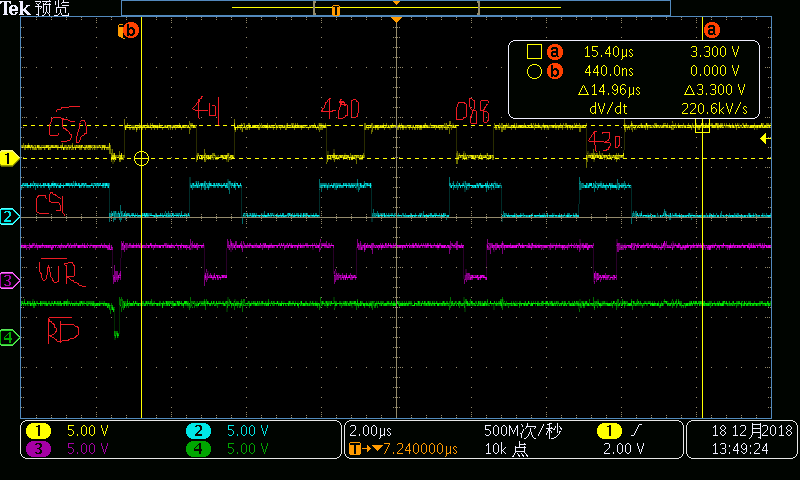

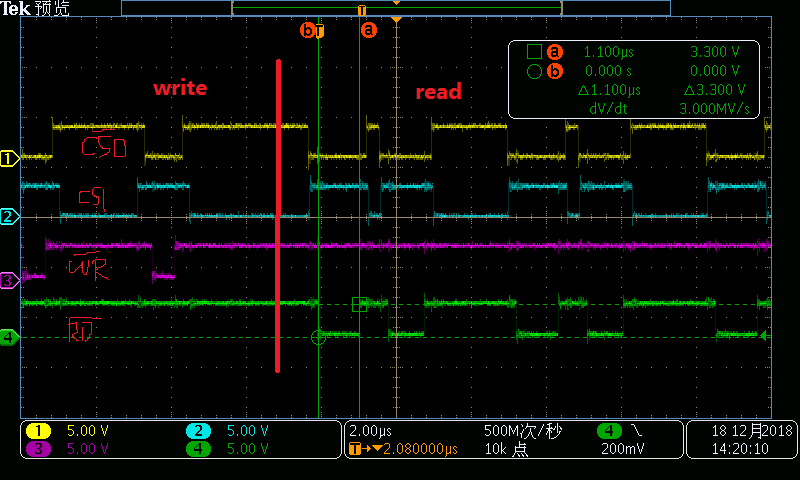

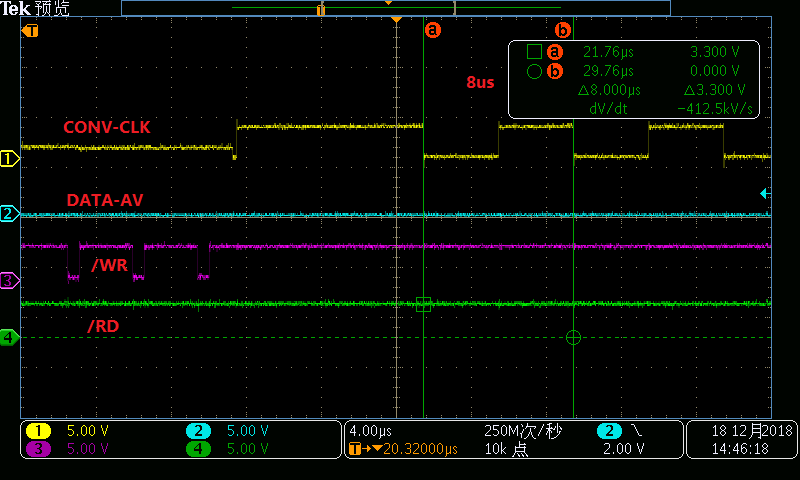

THS1206M-EVM is connected to TMS320F28335,when D0-D11 are assigned to GPIO2-GPIO13 and CS1 /CS0 /WR /RD connect to GPIO68 70 72 74 respectively. GPIO0 is set to get DATA_AVL signal and triger interrupt at rising edge.GPIO1 is set to control CONK_CLK/CONVST. We adopt internal reference REFP REFM. This is the basic connection pattern.

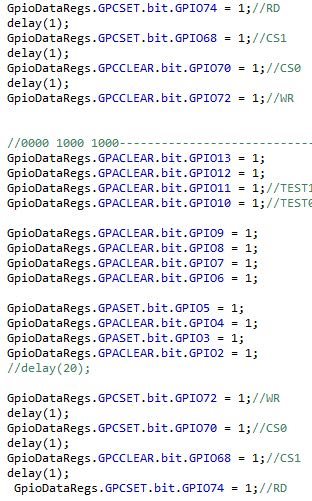

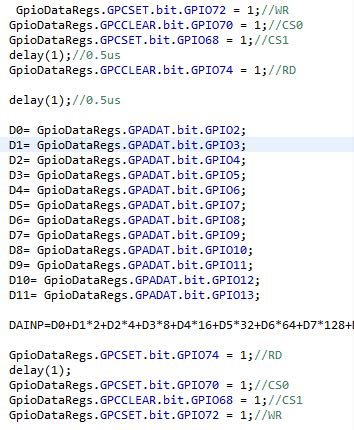

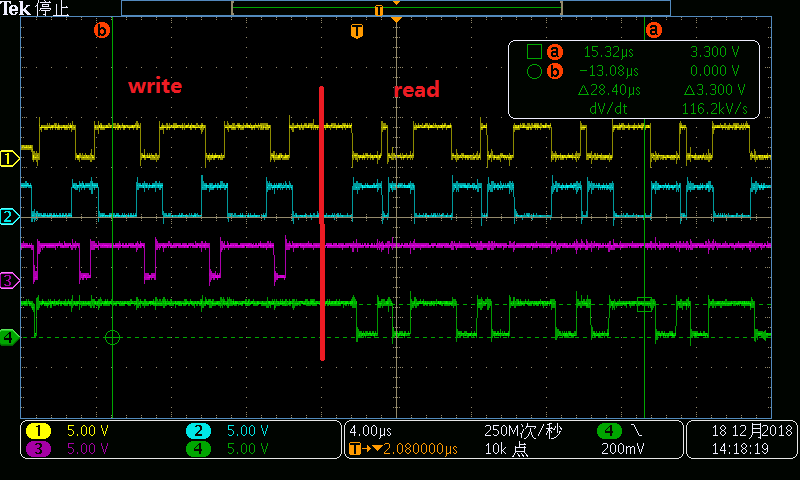

To configure CS1 /CS0 /WR /RD, we write 0x401,0x400,0x088,0x430 to D0-D11 successively. CONV_CLK signal is 10us 50%pwm. However,we can not get DATA_AVL signal. Therefore, we get to test it. First, when RBACK=1,we read two times in for circles and we get 0x088,0x430,which means the write and read option may be successful. Next,we set.TEST1、TEST0 to 01 10 11 to get in 'Test mode',but the value we read is zero which has no change. Therefore, what is wrong? why can not we get DATA_AVL signal or get in 'Test Mode'?