Other Parts Discussed in Thread: , ADC08D1500

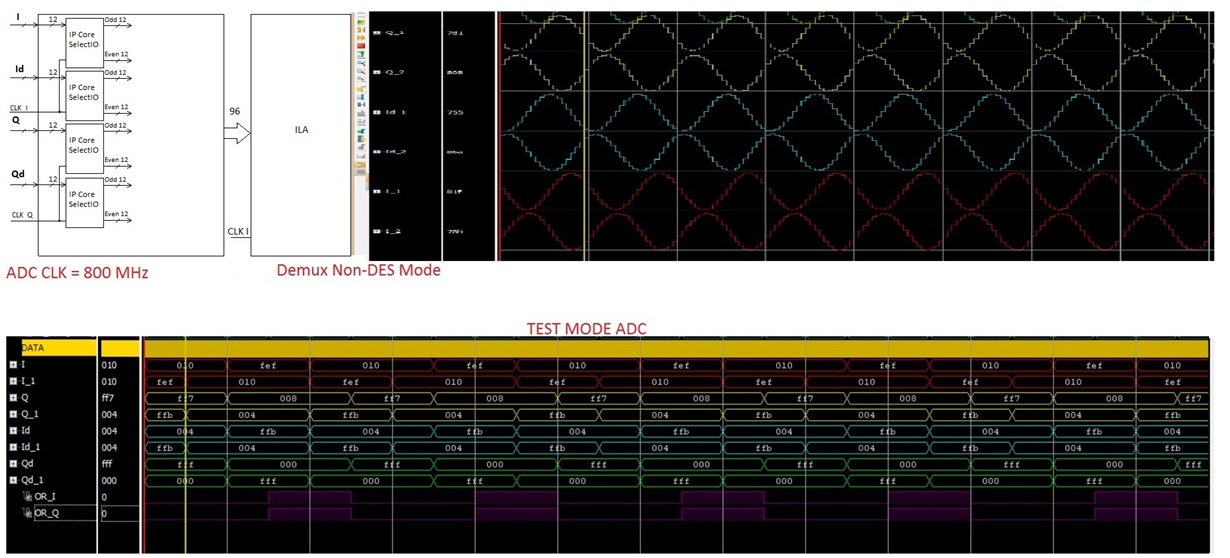

The ADC receives a clock frequency of 800 MHz. ADC Demux Non-DES Mode.

CAL_ADC = 0

DDRPH_ADC = 0

ECE_ADC = 0

CALDLY_ADC = 0

FSR_ADC = 0

NDM_ADC = 0

TPM_ADC = 0

PDI_ADC = 0

PDQ_ADC = 0

DES_ADC = 0

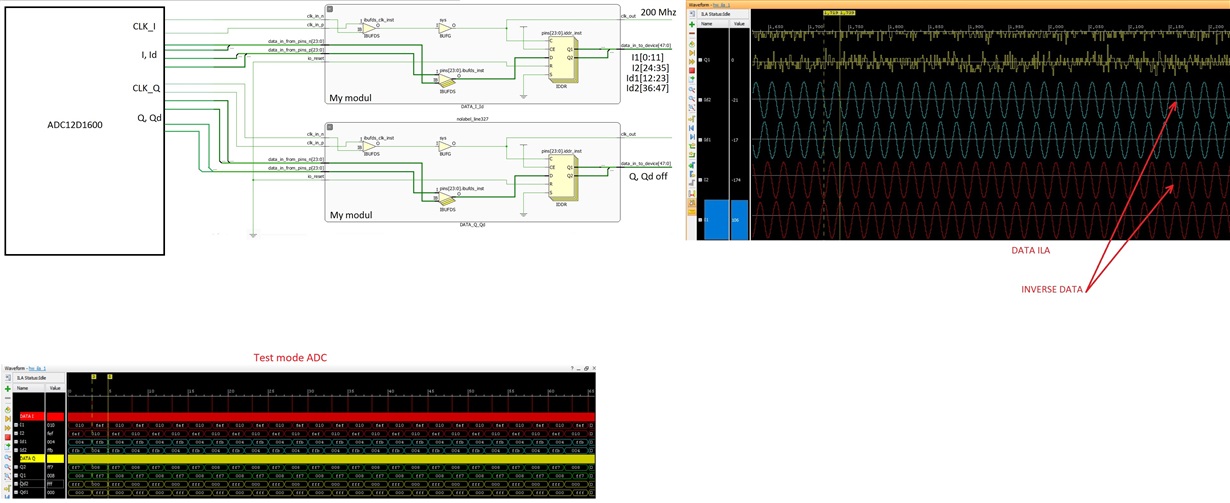

Configuration register 0x2010. CLK_I and CLK_Q 200 MHz. Data is sent to SelectIO. I connected to the output of SelectIO ILA. I get odd data inverted. ADC test mode data is correct.