Other Parts Discussed in Thread: DAC38J84

Setup Details :

- DAC37J82EVM board

- Xilinx VCU118 Demo board

- JESD204 v7.2.4 TX IP is instantiated

- JESD204B subclass 1

- LMFKS = 4, 2, 1, 30, 1

- 1 GSPS sampling rate, 250 MHz core clock, 10 Gbps line rate

Observations :

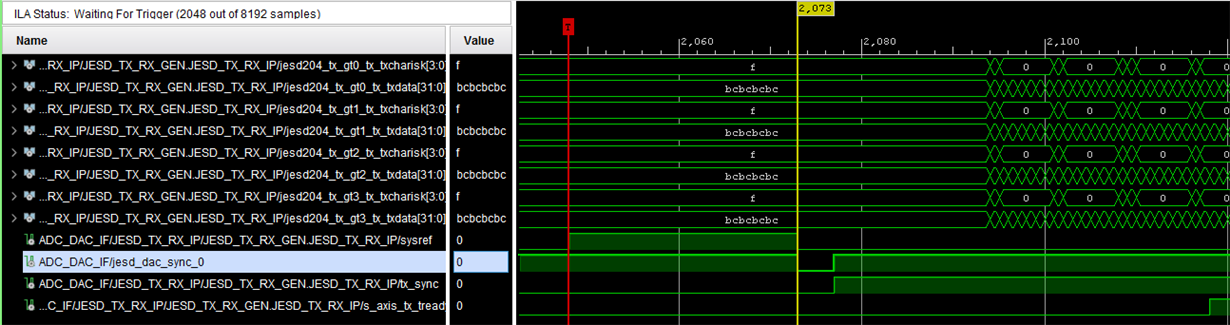

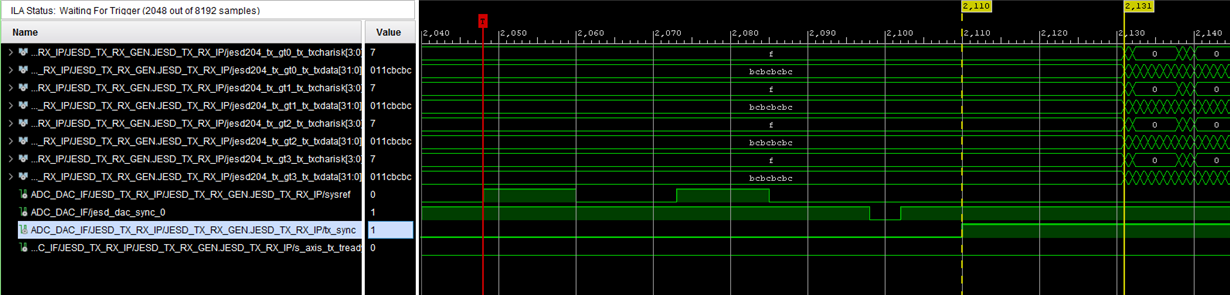

On most synchronization attempts, the DAC requests SYNC from the FPGA 130 ns after the rising edge of SYSREF is seen :

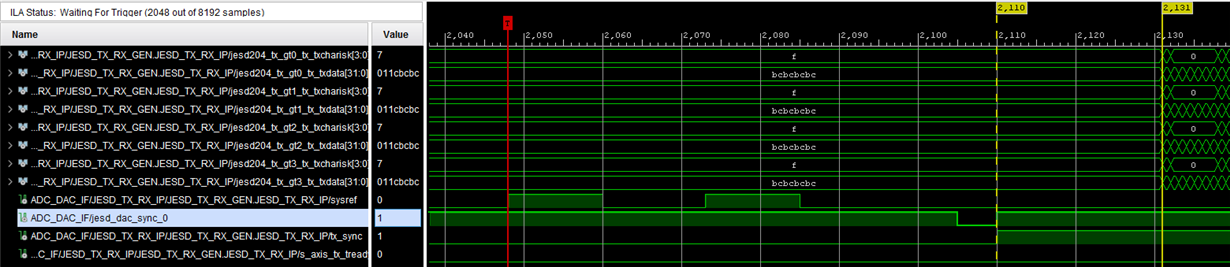

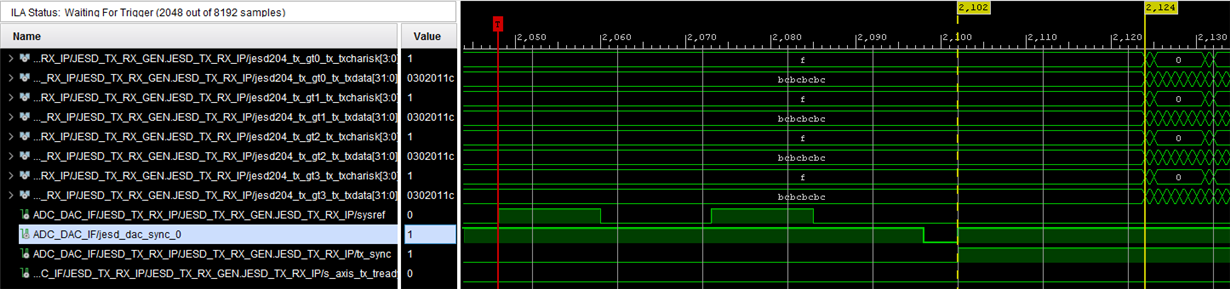

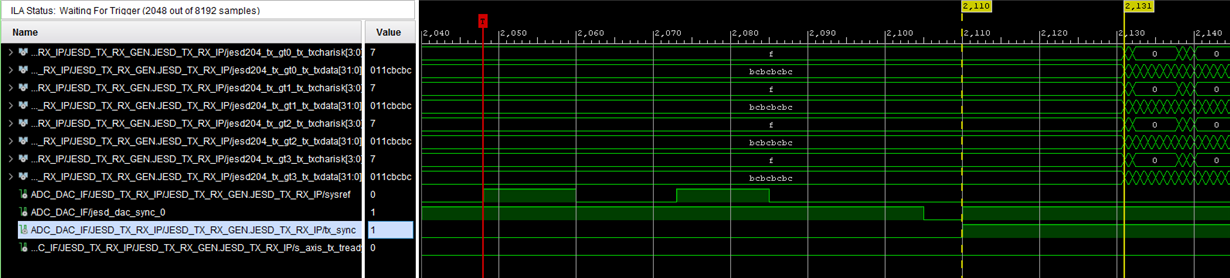

However on a minority of synchronization attempts (5% - 10% of tries), the DAC requests SYNC from the FPGA 100 ns after the rising edge of SYSREF is seen :

I've verified on a high-speed scope that the DAC is given 2 ns of setup time to capture SYSREF, so I don't believe that's the issue.

This leaves us with a variance in synchronization time of 1 LMFC period (30 ns in our case), and I'm struggling to understand why this would be. Based on what I have learned about the JESD204B protocol so far, I thought that the rising edge of SYSREF was supposed to realign the LMFC in all connected devices and that ILA generation begins on the next LMFC zero crossing after SYNC has been deasserted, as indicated in this image :

How does the DAC decide on which LMFC edge to request SYNC from the FPGA? Is there a way to force the DAC to use the same LMFC edge for SYNC requests every time?

Thank you

-Branden