As described in the subject I'm using the ADS62P42 in CMOS MUX Mode.

I have to mention that all 3 parallel control pins are at GND to have serial (SPI) config only and that I put in register 14 the power down mode at 111 (MUX mode)

Here are the content of my spi registers

register 00 0x02 //at the beginning to reset everything

register 10 0x00

register 11 0x0c

register 12 0x00

register 13 0x10

register 14 0x87 = I put in register 14 the power down mode at 111 (MUX mode)

register 16 0x00

register 17 0x0c

register 18 0x00

register 19 0x00

register 1A 0x80

register 1B 0x03

register 1D 0x00

After SPI set-up register programming I'm receiving the result for Input B in MUX mode (Input B and Input A) in very short laps of the time.

However next read of Input B (after few seconds) I looking that it was no more in CMOS MUX Mode than it is switched to normal mode itself like it is make Reset internally ...??

The ADS62P42 could not keeping SPI setting of CMOS MUX mode long time ... ???

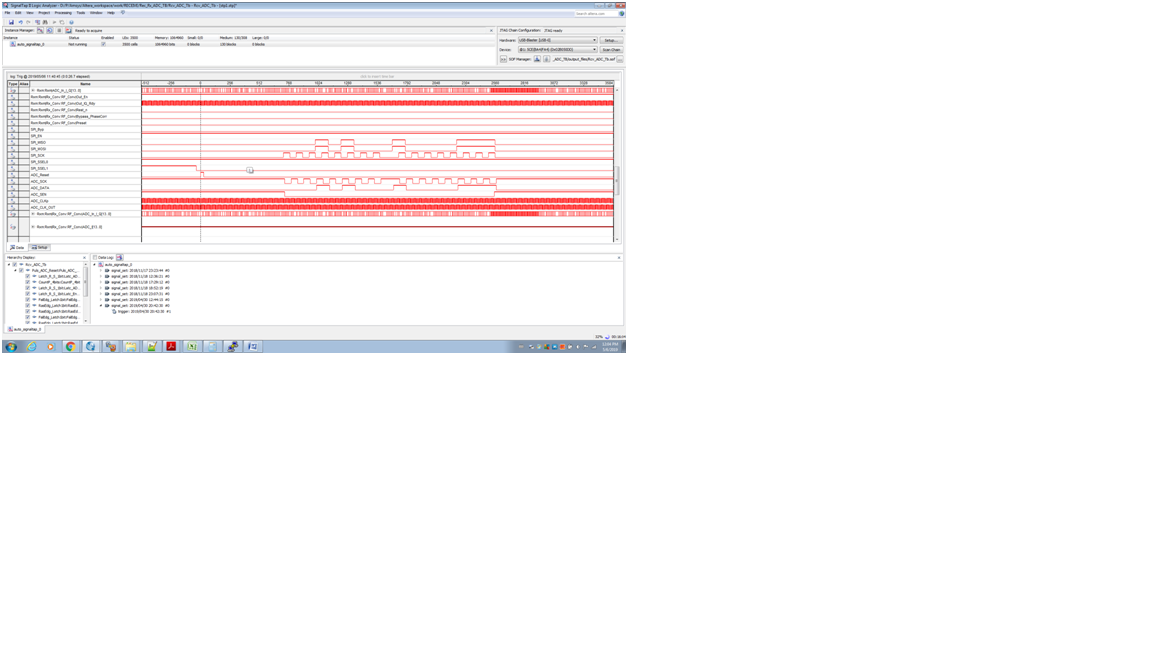

You can see Signal TAP capture figure - the input finished with ADC_in_I_Q[13..0] -- in CMOS MUX Mode I received in this input double frequency signal.

I tried again few times and the result is the same each time ... ?

Please, would you give a solution of this issue ?

Luc Stan