Hi,

According to the datasheet the converters need maximum of 200 us for valid data after power down.

Since we want to use PDN feature I measured the wake up time, and it seems to be much longer.

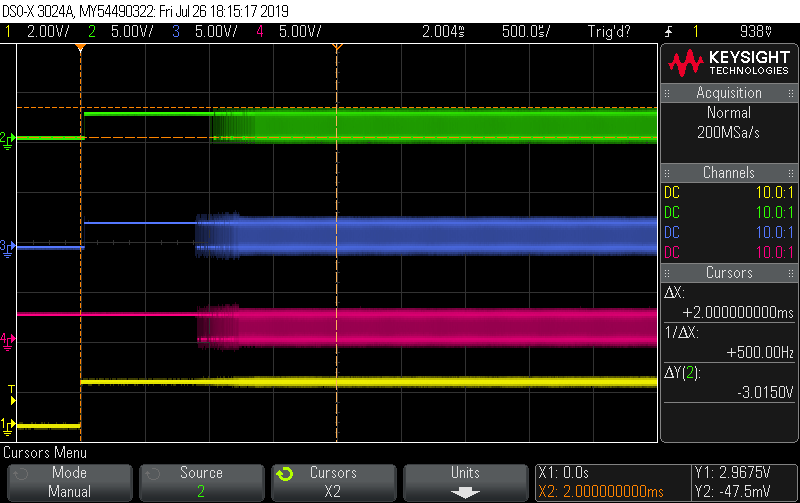

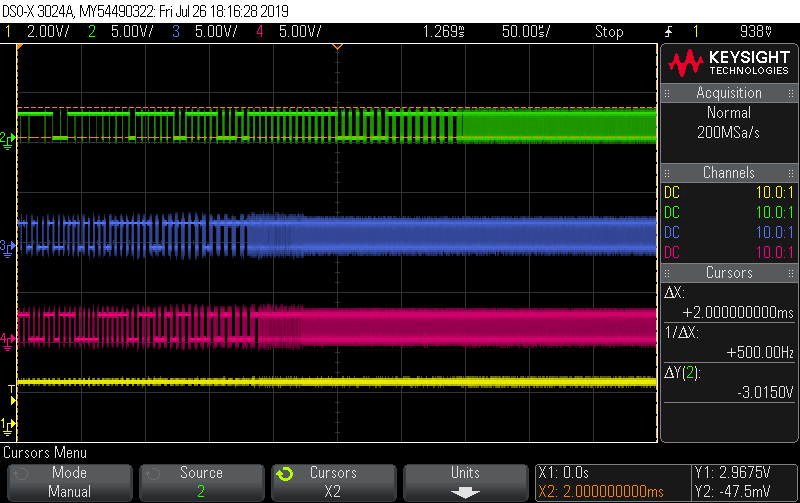

Channel 1 (yellow) shows our active low reset, which is routed to each AD converters (after inverted). ADCs start to generate frame clock after approximately

1 ms, but it is followed by a ca. 500 us period, when the frame clock is right. See the picture below.

This is something we can live with, but would like to know what maximum wake up time we should design our logic to handle this transition?

Thank you.

Best regards,

Peter