Greeting everybody,

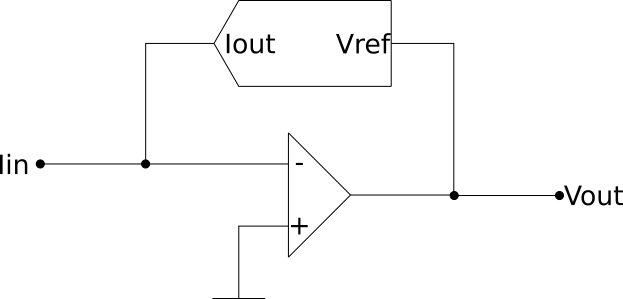

I am looking to design an adjustable current-to-voltage converter circuit. The basic circuit is just a regular Op-Amp style IVC, where a feedback resistor mediates the conversion. Since my design should run on 3.3 V dual supply and be quite compact I was trying to use an mDAC device. However I am getting some unexpected results. The mDACs Vref - Iout path replaces the feedback resistor on the Op-Amp. If I leave the input of the converter open (aka. 0 A flowing in), I would expect an output voltage of 0 V. However, it seems that the Op-Amp still needs to provide a voltage to keep the negative input at 0 V. This voltage is furthermore depending on the code that the mDAC is set to.

My thoughts were, that the mDAC is an R2R ladder and as such mostly behaves like a resistor. Seemingly that notion was wrong and so I wanted to ask, if there is something I am not seeing or not aware of, or if such a configuration can simply not work and why.

Thanks in advance,

FB.