Hi all,

I'm trying to get the DAC39J84 to work into 4421 configuration. However after configuring the device and start up the JESD links I got no data at the analog outputs.

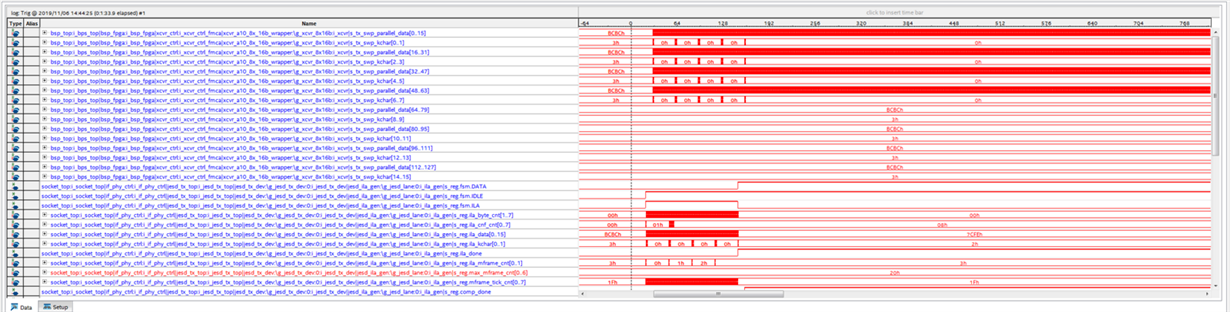

After configuration I can verify that the active SERDES do not have errors (registers 0x64 to 0x68) and I can see in signal tap that the JESD links have been initialized properly:

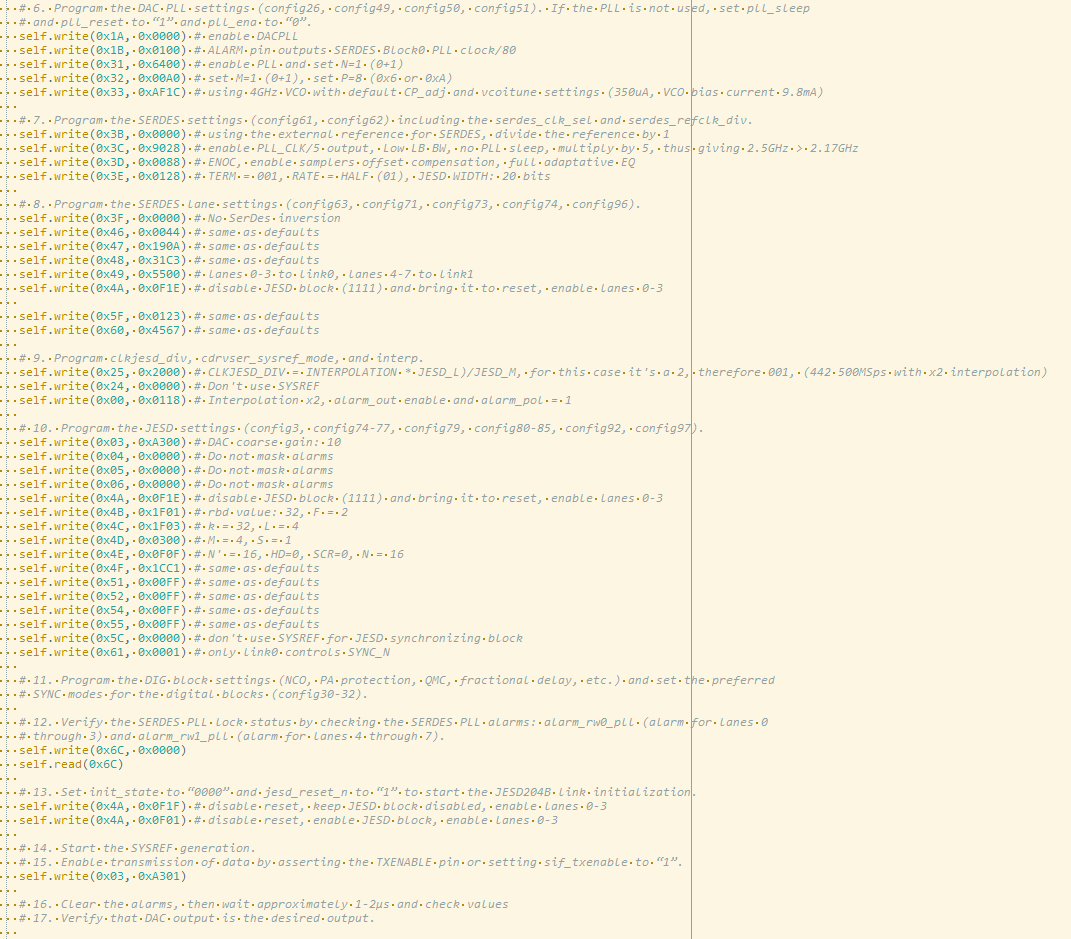

The configuration setup is as follows:

I really don't know what I'm doing wrong. Probably is something reasonably simple.

Thanks in advance.

DAC39J84 configuration JESD settings: 4421 Fin = Fs: 500MHz, interpolation x2 DACPLL enabled, N = 1, M = 1, P = 8, VCO @ 4GHz SERDES: 5Gbps, half rate PLL @ 2.5GHz Read 0X118 from DAC39J84::0X0000 Read 0X03 from DAC39J84::0X0001 Read 0X2002 from DAC39J84::0X0002 Read 0XA301 from DAC39J84::0X0003 Read 0X00 from DAC39J84::0X0004 Read 0X00 from DAC39J84::0X0005 Read 0X00 from DAC39J84::0X0006 Read 0X2501 from DAC39J84::0X0007 Read 0X00 from DAC39J84::0X0008 Read 0X00 from DAC39J84::0X0009 Read 0X00 from DAC39J84::0X000A Read 0X00 from DAC39J84::0X000B Read 0X400 from DAC39J84::0X000C Read 0X400 from DAC39J84::0X000D Read 0X400 from DAC39J84::0X000E Read 0X400 from DAC39J84::0X000F Read 0X00 from DAC39J84::0X0010 Read 0X00 from DAC39J84::0X0011 Read 0X00 from DAC39J84::0X0012 Read 0X00 from DAC39J84::0X0013 Read 0X00 from DAC39J84::0X0014 Read 0X00 from DAC39J84::0X0015 Read 0X00 from DAC39J84::0X0016 Read 0X00 from DAC39J84::0X0017 Read 0X00 from DAC39J84::0X0018 Read 0X00 from DAC39J84::0X0019 Read 0X00 from DAC39J84::0X001A Read 0X100 from DAC39J84::0X001B Read 0X00 from DAC39J84::0X001C Read 0X00 from DAC39J84::0X001D Read 0X1111 from DAC39J84::0X001E Read 0X1140 from DAC39J84::0X001F Read 0X00 from DAC39J84::0X0020 Read 0X00 from DAC39J84::0X0021 Read 0X1B1B from DAC39J84::0X0022 Read 0XFFFF from DAC39J84::0X0023 Read 0X00 from DAC39J84::0X0024 Read 0X2000 from DAC39J84::0X0025 Read 0X00 from DAC39J84::0X0026 Read 0X00 from DAC39J84::0X0027 Read 0X03 from DAC39J84::0X0028 Read 0XFFFF from DAC39J84::0X0029 Read 0X00 from DAC39J84::0X002A Read 0X00 from DAC39J84::0X002B Read 0X00 from DAC39J84::0X002C Read 0X00 from DAC39J84::0X002D Read 0XFFFF from DAC39J84::0X002E Read 0X04 from DAC39J84::0X002F Read 0X00 from DAC39J84::0X0030 Read 0X6404 from DAC39J84::0X0031 Read 0XA0 from DAC39J84::0X0032 Read 0XAF1C from DAC39J84::0X0033 Read 0X00 from DAC39J84::0X0034 Read 0X00 from DAC39J84::0X0035 Read 0X00 from DAC39J84::0X0036 Read 0X00 from DAC39J84::0X0037 Read 0X00 from DAC39J84::0X0038 Read 0X00 from DAC39J84::0X0039 Read 0X00 from DAC39J84::0X003A Read 0X00 from DAC39J84::0X003B Read 0X9028 from DAC39J84::0X003C Read 0X88 from DAC39J84::0X003D Read 0X128 from DAC39J84::0X003E Read 0X00 from DAC39J84::0X003F Read 0X00 from DAC39J84::0X0040 Read 0X00 from DAC39J84::0X0041 Read 0X00 from DAC39J84::0X0042 Read 0X00 from DAC39J84::0X0043 Read 0X00 from DAC39J84::0X0044 Read 0X00 from DAC39J84::0X0045 Read 0X44 from DAC39J84::0X0046 Read 0X190A from DAC39J84::0X0047 Read 0X31C3 from DAC39J84::0X0048 Read 0X5500 from DAC39J84::0X0049 Read 0XF01 from DAC39J84::0X004A Read 0X1F01 from DAC39J84::0X004B Read 0X1F03 from DAC39J84::0X004C Read 0X300 from DAC39J84::0X004D Read 0XF0F from DAC39J84::0X004E Read 0X1CC1 from DAC39J84::0X004F Read 0X00 from DAC39J84::0X0050 Read 0XFF from DAC39J84::0X0051 Read 0XFF from DAC39J84::0X0052 Read 0X00 from DAC39J84::0X0053 Read 0XFF from DAC39J84::0X0054 Read 0XFF from DAC39J84::0X0055 Read 0X00 from DAC39J84::0X0056 Read 0XFF from DAC39J84::0X0057 Read 0XFF from DAC39J84::0X0058 Read 0X00 from DAC39J84::0X0059 Read 0XFF from DAC39J84::0X005A Read 0XFF from DAC39J84::0X005B Read 0X00 from DAC39J84::0X005C Read 0X00 from DAC39J84::0X005D Read 0X00 from DAC39J84::0X005E Read 0X123 from DAC39J84::0X005F Read 0X4567 from DAC39J84::0X0060 Read 0X01 from DAC39J84::0X0061 Read 0X00 from DAC39J84::0X0062 Read 0X00 from DAC39J84::0X0063 Read 0X00 from DAC39J84::0X0064 Read 0X00 from DAC39J84::0X0065 Read 0X00 from DAC39J84::0X0066 Read 0X00 from DAC39J84::0X0067 Read 0XA802 from DAC39J84::0X0068 Read 0XFF0F from DAC39J84::0X0069 Read 0XFF0F from DAC39J84::0X006A Read 0X7C03 from DAC39J84::0X006B Read 0X06 from DAC39J84::0X006C Read 0X90 from DAC39J84::0X006D Read 0X00 from DAC39J84::0X006E Read 0X00 from DAC39J84::0X006F Read 0X00 from DAC39J84::0X0070 Read 0X00 from DAC39J84::0X0071 Read 0X00 from DAC39J84::0X0072 Read 0X00 from DAC39J84::0X0073 Read 0X00 from DAC39J84::0X0074 Read 0X00 from DAC39J84::0X0075 Read 0X00 from DAC39J84::0X0076 Read 0X00 from DAC39J84::0X0077 Read 0X00 from DAC39J84::0X0078 Read 0X00 from DAC39J84::0X0079 Read 0X00 from DAC39J84::0X007A Read 0X00 from DAC39J84::0X007B Read 0X00 from DAC39J84::0X007C Read 0X00 from DAC39J84::0X007D Read 0X00 from DAC39J84::0X007E Read 0X800A from DAC39J84::0X007F