Hi,

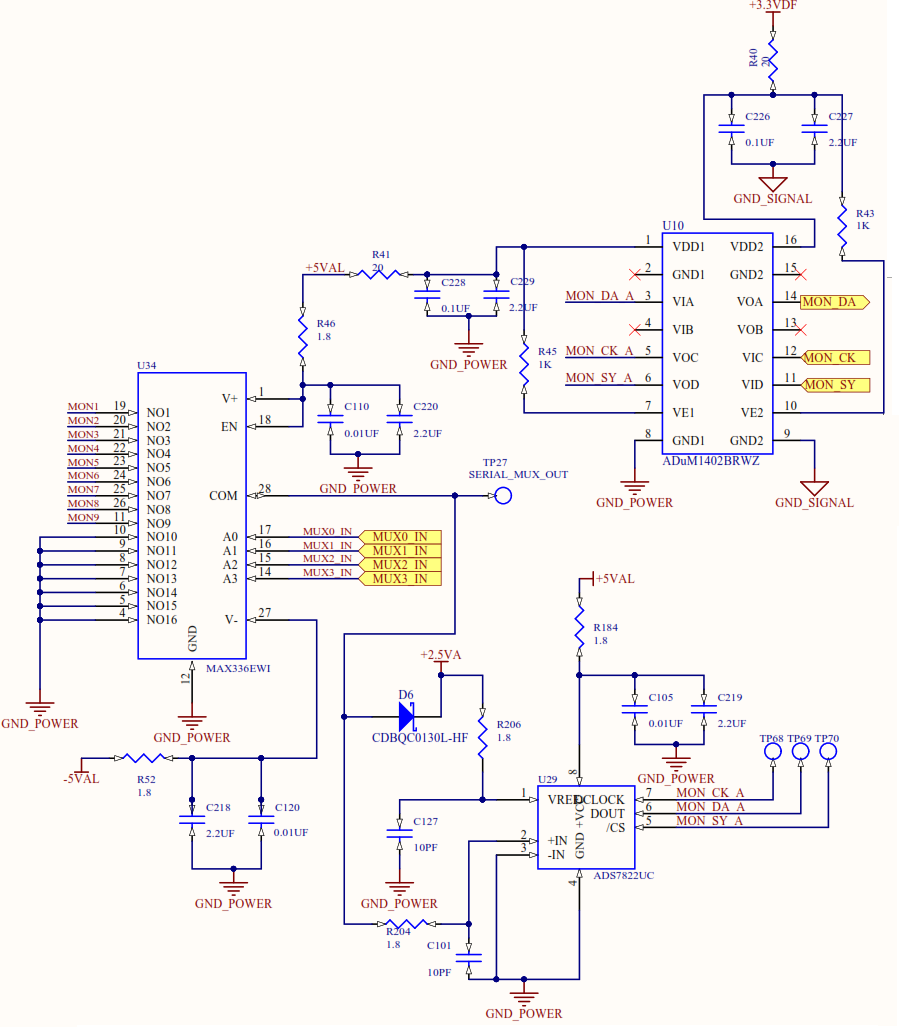

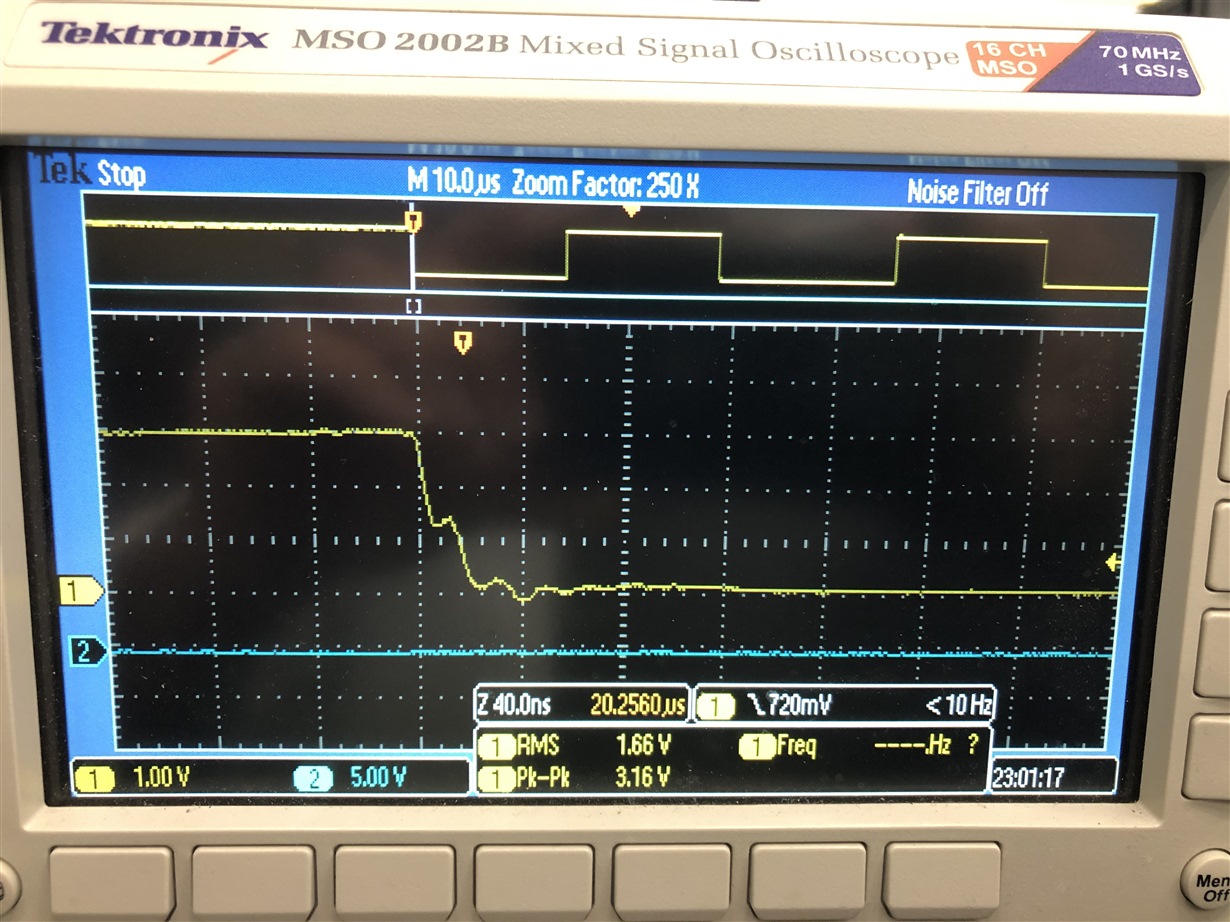

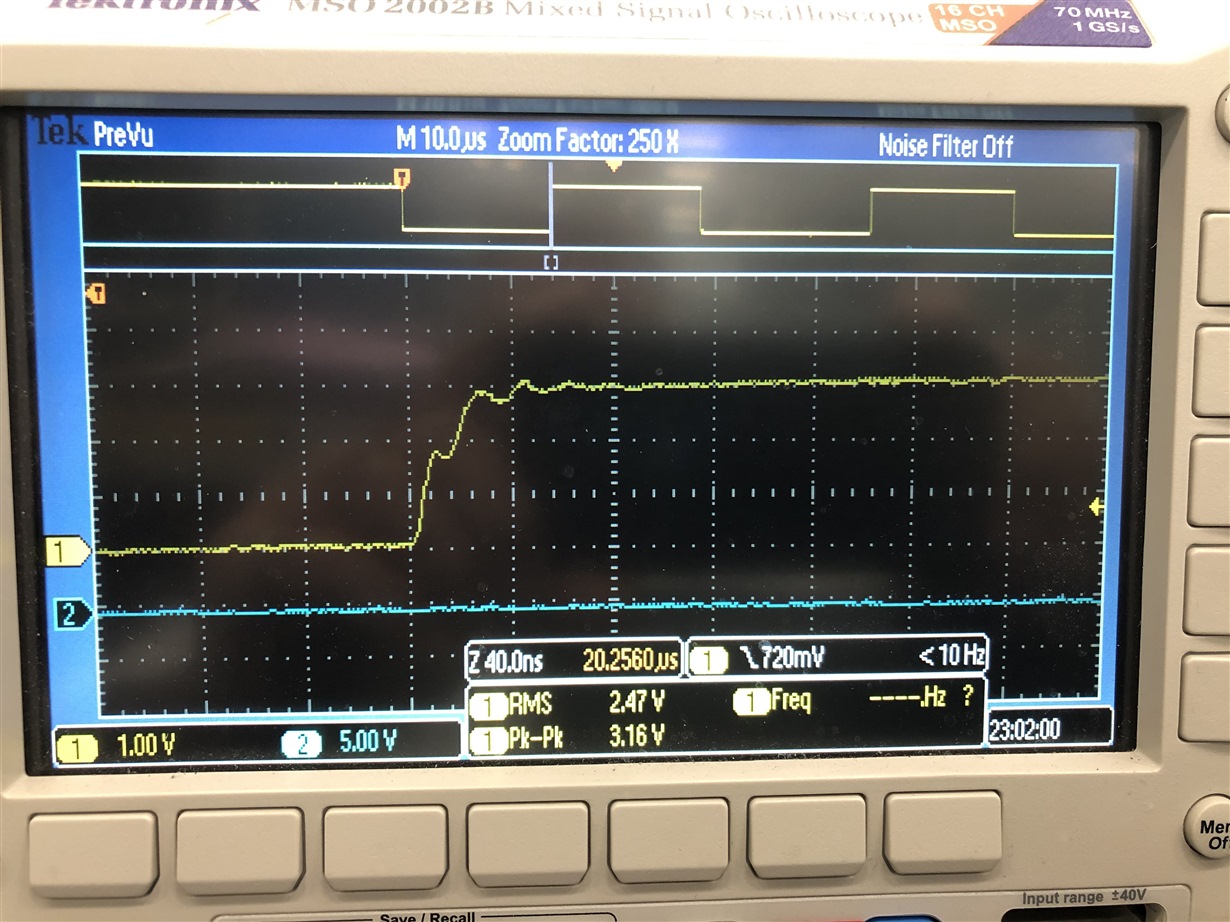

This chip does not behave at all as per its data sheet. The clocking diagram is not the same! The first two clock cycles conversion time are missing! Data line follows clock in some places and data received is NOT as per +IN and -IN analogue inputs. Please advise. Thanks.

M.A.