Other Parts Discussed in Thread: ADS54J60

Hi,

I'm currently using 8-2-2-4 mode with the attached configuration setting and would like some help addressing two questions.

1. Is my configuration setting right for 8-2-2-4? I'm using the local onboard oscillator as reference clock.

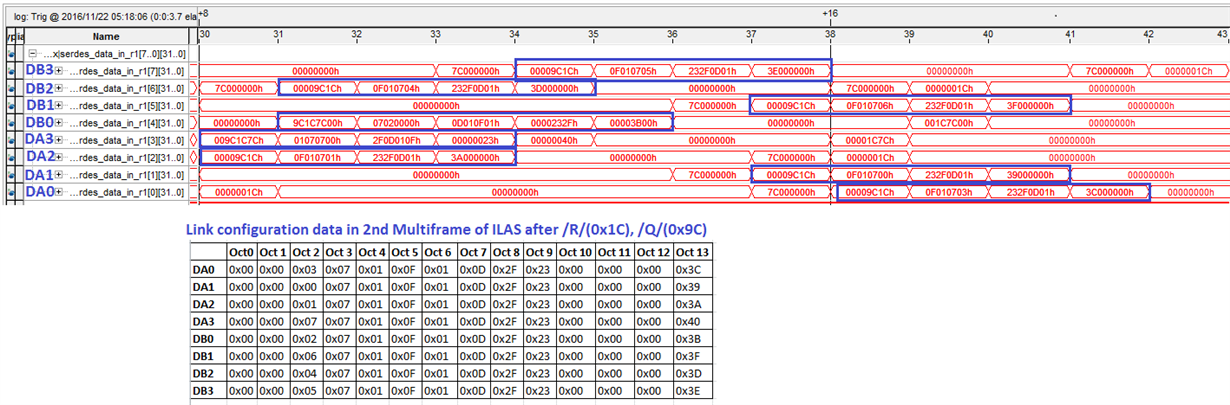

2. On the FPGA side my parallel data bus at the other end of the 8-lane JESD204B interface is 256-bit, 32-bit per lane. I'm currently trying to figure out how the 16-bit samples from both channel A and B are supposed to be showing up. I'm currently assuming that for every 32-bit per lane, the samples are aligned on 16-bit boundary so basically one sample would be in bits 31-16 and another sample would be in bits 15-0. Is this assumption correct? Also I tried to turn on FOVR to force the LSB to 0 if my input signals are low and below the FOVR range so that this can help give more insights on any other potential byte-swap in the data representation but with 16-bit boundary assumption, this is not working and I don't know if it's alignment or if the FOVR setup is not working.

Thanks in advance for the help,

Tyler