Hi,

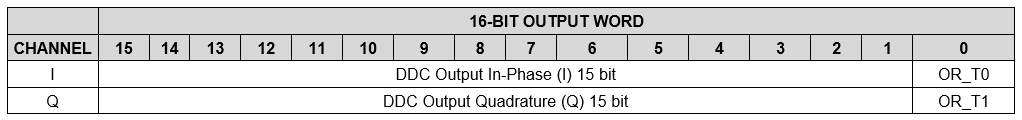

I'm using ADC12J1600 to sample the data processed by KC705. I have some questions about the output data format of ADC12J1600. Since I'm setting the ADC to "decimation by 4" mode, I've learned about the data format of the DDC should be like this:

My question is, considering the raw sampled data of ADC12J1600 has 12bits, do all 15 bits here represent the value of data after decimation? Is one of the 15 bits the sign bit?

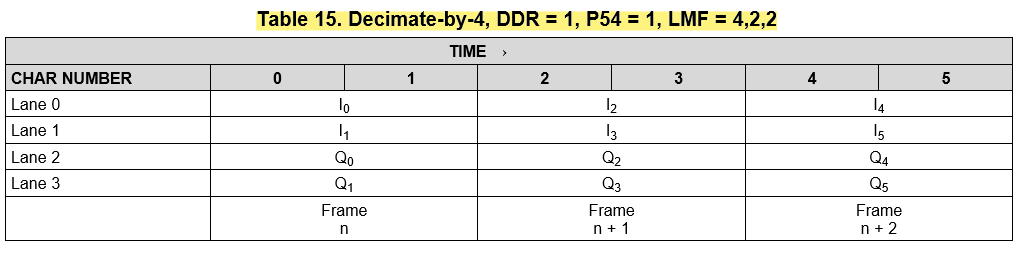

Another thing is, the parameters of the serial link I set should be LMFS = 4222. Here's the table about this:

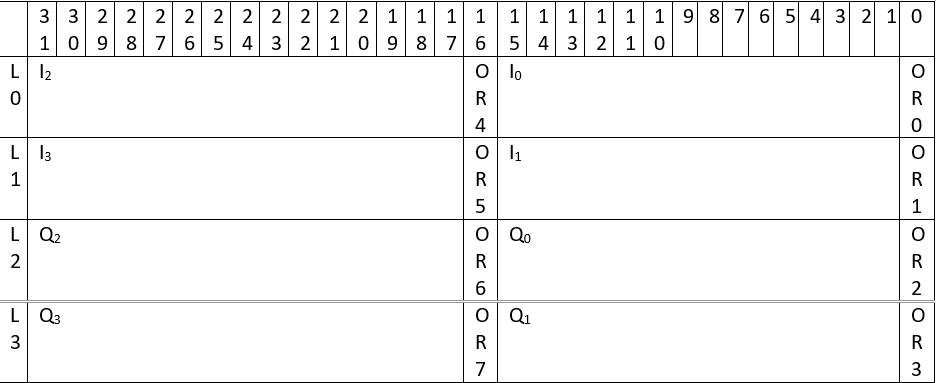

I've downloaded the JESD204B demo project onto FPGA, and I've checked the data format of the receiver. The data of each lane has 32 bits. Could you provide some advice about data mapping here?

Thanks in advance for your help, I'm looking forward to your reply.

Best,

Haotian.