Other Parts Discussed in Thread: DAC5675A

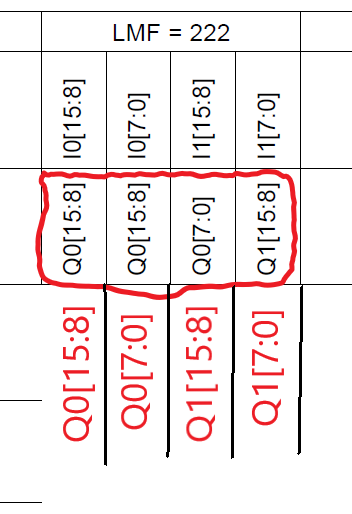

Is there a typo in the datasheet for the frame assembly format for LMF 222 ? There is no mention of Q1[7:0], whereas Q0[15:8] appears twice.

Is the frame format written in red for Lane 1 in the attached photo correct ?

I am migrating from an LVDS based DAC (DAC5675A) design to JESD DAC (DAC37J82) design. The sequence of the complex data sent to the LVDS DAC was I_P -> Q_P -> Q_N -> I_N

I_P <= {~I [15], I [14:0]};

I_N <= {I [15], ~I [14:0]};

Q_P <= {~Q [15], Q [14:0]};

Q_N <= {Q [15], ~Q [14:0]};

Is the below frame assembly format correct for this implementation ?

| Lane 0 | I_P[15:8] | I_P[7:0] | Q_N[15:8] | Q_N[7:0] |

| Lane 1 | Q_P[15:8] | Q_P[7:0] | I_N[15:8] | I_N[7:0] |