Other Parts Discussed in Thread: LMK04828, LMX2592

Hi,

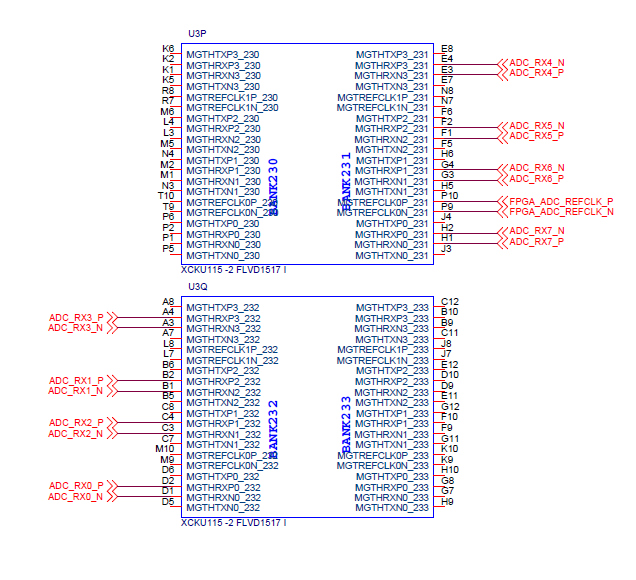

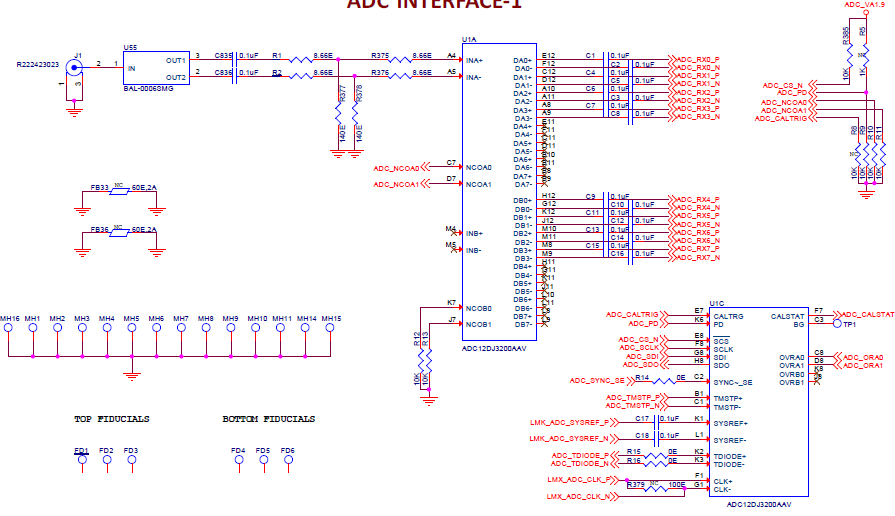

We are using ADC12DJ3200 operated in JMODE 5 for 5 GSPS. We are operating the serdes at 6.25 gbps x 8 lanes.

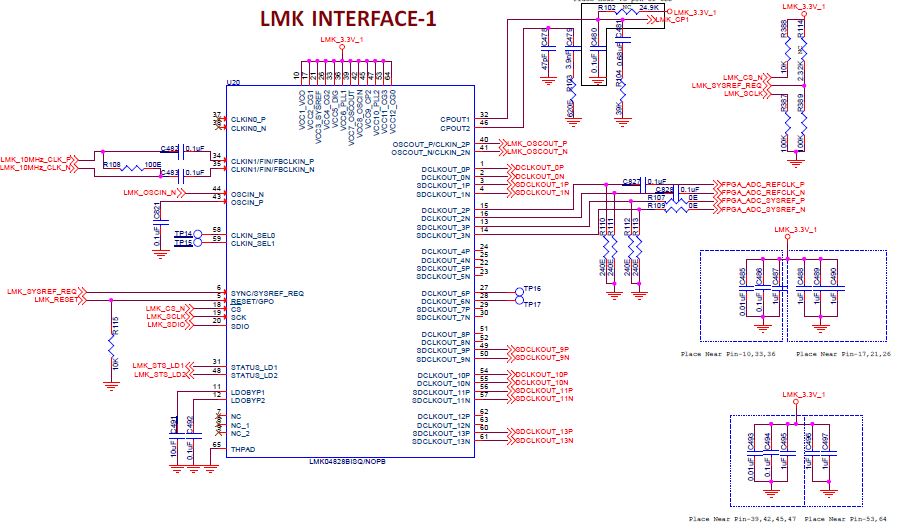

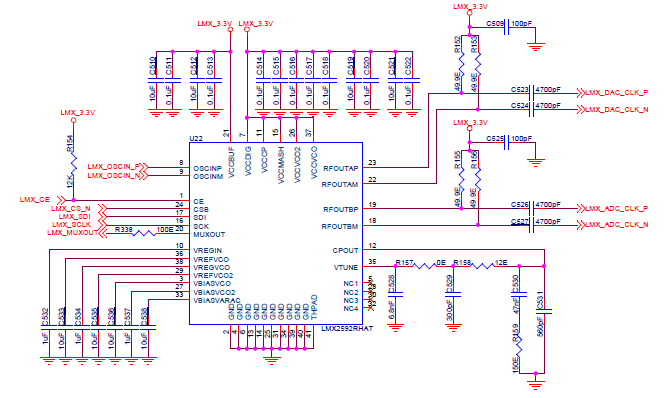

Sysref (19.53125 MHz) and dclk (156.25 MHz) for FPGA generated from LMK04828 and ADC sampling clock generated (2.5 GHz) from LMX2592.

ADC sysref also generated from LMK04828 (19.53125 MHz) for F=1 and K=32. Both FPGA and ADC are operated with same settings.

We have monitored dclk and sysref for FPGA, we are operating in LVDS and within the FPGA specs for receiving.

The sysref clock to ADC is operated with LVPECL(1600) from LMK04828, circuit to similar to ADC eval boad HSP001.

We are able to read and write the ADC. ADC debug status register reads 0x1C. ADC seems to be responding ok. But the Sync is low.

We are using PHY + JESP IP, FPGA side receives some junk data not 0xBC.

Please help, we are struck at this stage.

Regards,

Rajesh khanna