We are looking for an ADC for our RF signal 1100MHz (under sampling) for the data bandwidth of 20MHz.

We need the following specifications for ADC to do under sampling,

1. FPBW >= 1100MHz

2. Sampling >= 150MHz

3. Resolution = 14bit or above

4. SNR at 1100MHz >=60dB @150MSPS sampling

5. Power dissipation < 1.5W

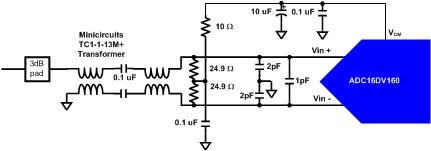

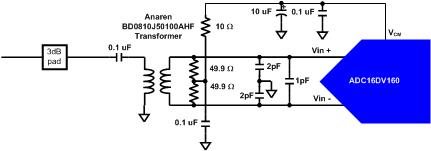

For the above requirement we have checked your ADC : ADC16DV160 which meets the all the requirement. But we are unable to find the SNR Value for our Frequency of 1100MHz from your datasheet. (SNR data available upto 200MHz input frequency)

Kindly share the SNR data at 1100MHz to proceed us further. We are looking or an SNR >=60dB at our 1100MHz frequency.

Note: We will put one more channel in idle mode.

Regards,

Sugumar K

India.