Hi,

The behavior of the ADS7947 is not as expected in our custom board.

【Question】

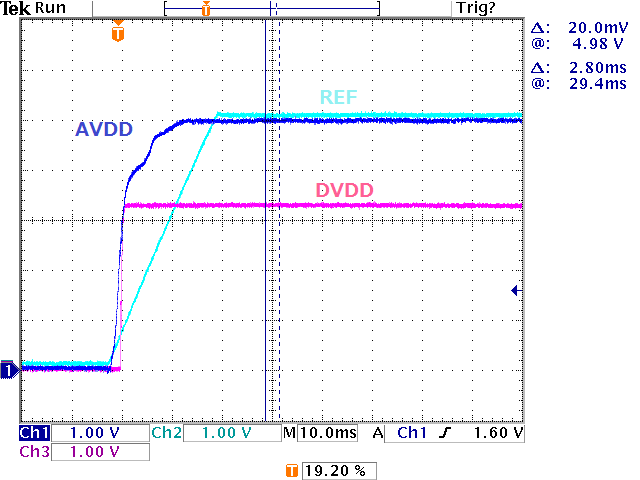

Is there any prescriptions for up sequences at power on to the voltage applied to the AVDD pin and DVDD pin and REF pin?

【Issue】

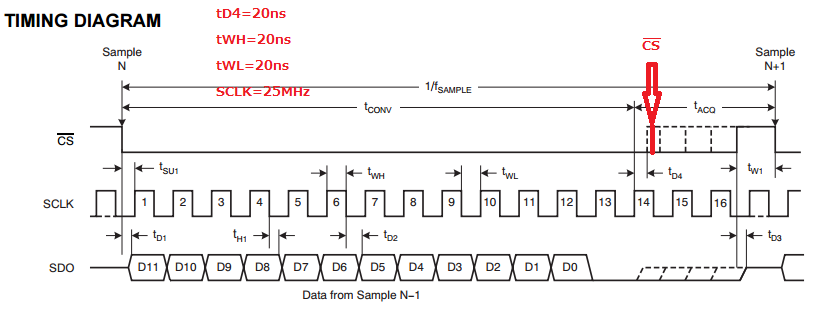

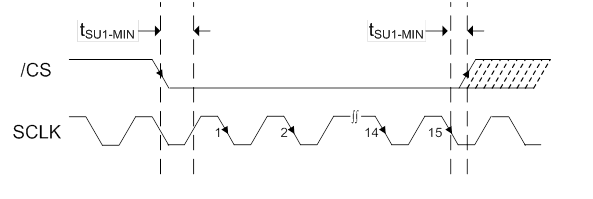

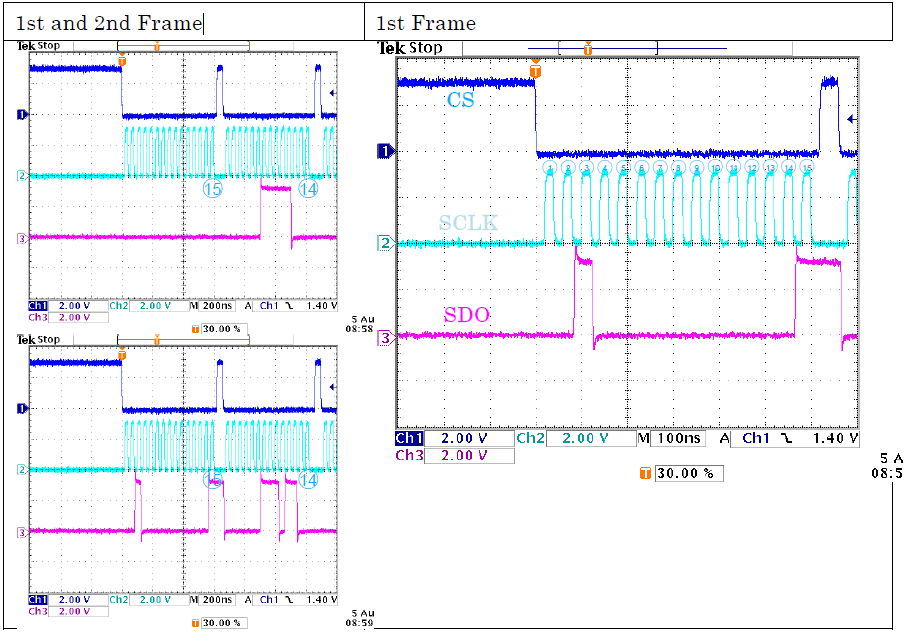

CS and SCLK are sent, but SDO data are not outputted.

When the AVDD launch slower than DVDD, it works fine.

【Settings】

AVDD=5V、DVDD=3.3V、REF=5V

PDEN=0V、

CS…pullup to 3.3V at startup

CHSEL…Hi-Z at start up,ch will be changed 1 second later of a startup.

Insert a 4.7μF capacitor between REF and REFGND

Best regards,

Seishin