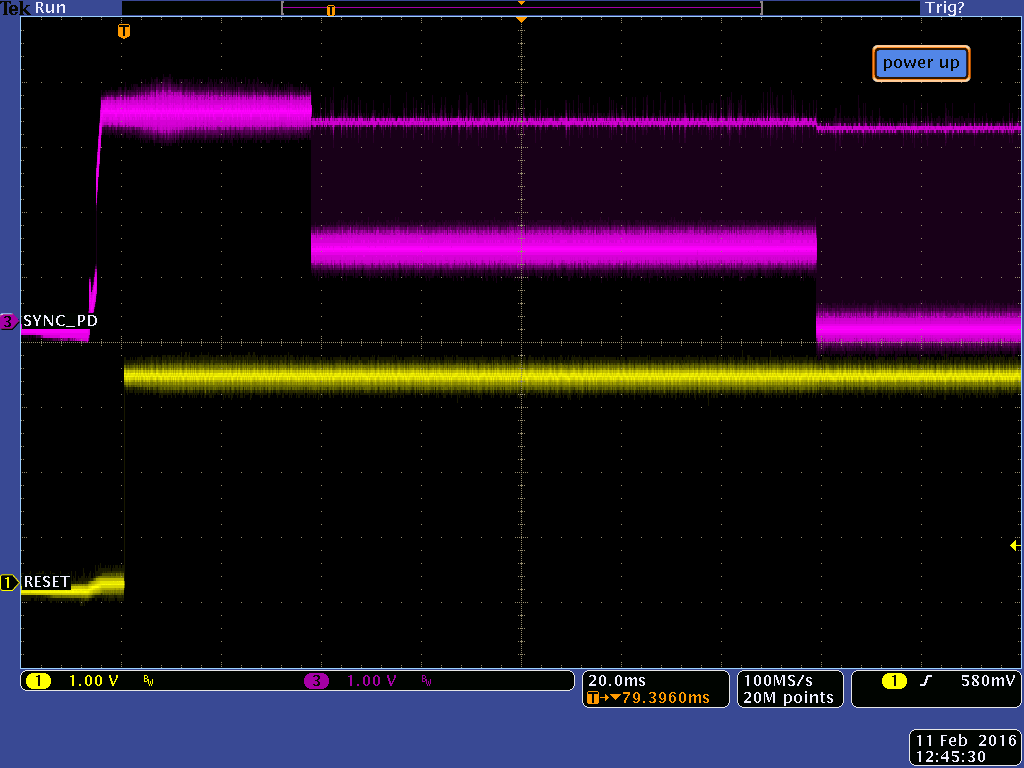

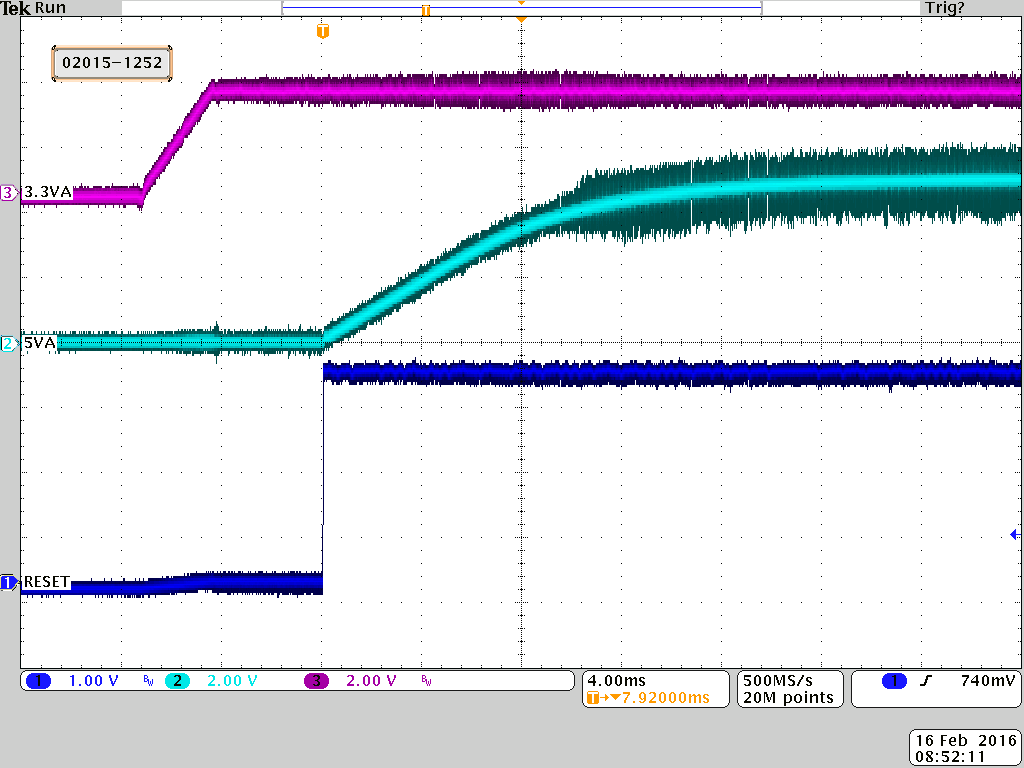

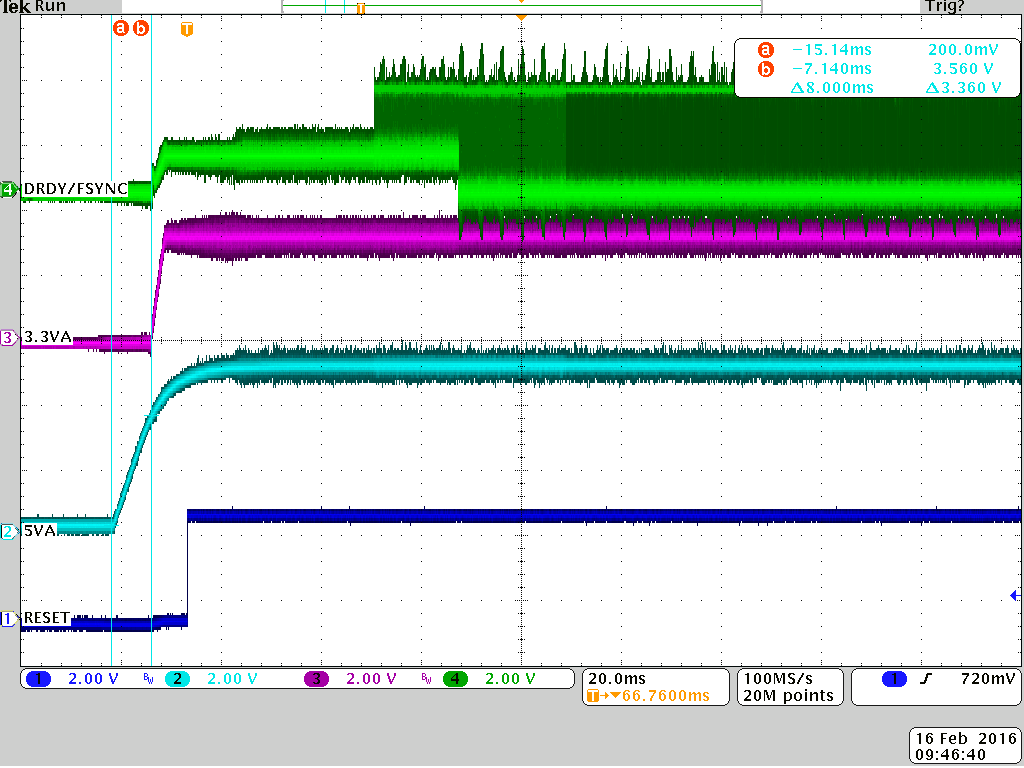

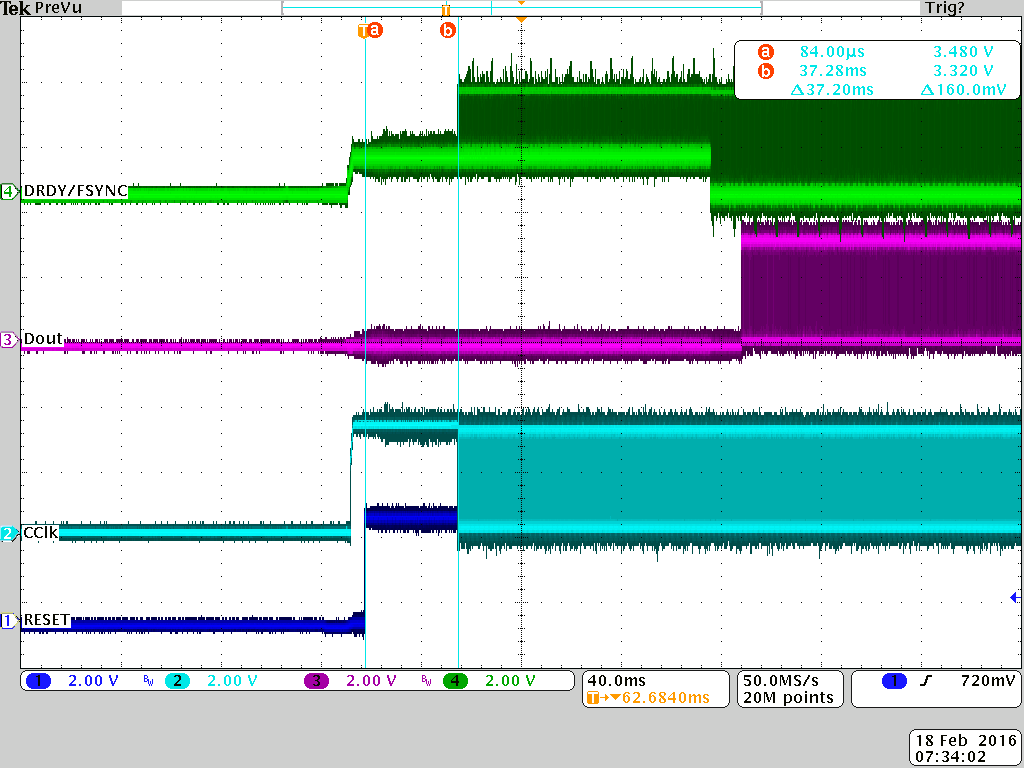

I am using 6 ADS1271 with gating on the frame sync signal to pairs of converters. The FORMAT and MODE pins are tied (through a resistor) to 3.3V. The output of a SN74LVC08A gate drive the FSYNC line on pairs of converters, with one input a frame sync signal from a 6713 DSP and the other input a dedicated I/O pin. After turning on the clocks, the FSYNC/DRDY line appears to be in DRDY mode, the signal does not return to ground, and has the FSYNC signal superimposed on it. The length of 'contention' is directly related to the CLK rate. I am assuming the DRDY is active until the SPI mode power up sequence of filling the filters is complete and a reading is ready, then the converter is going to frame sync mode.

The question: what is required to get the FSYNC/DRDY pin into frame sync mode? Is this a feature?

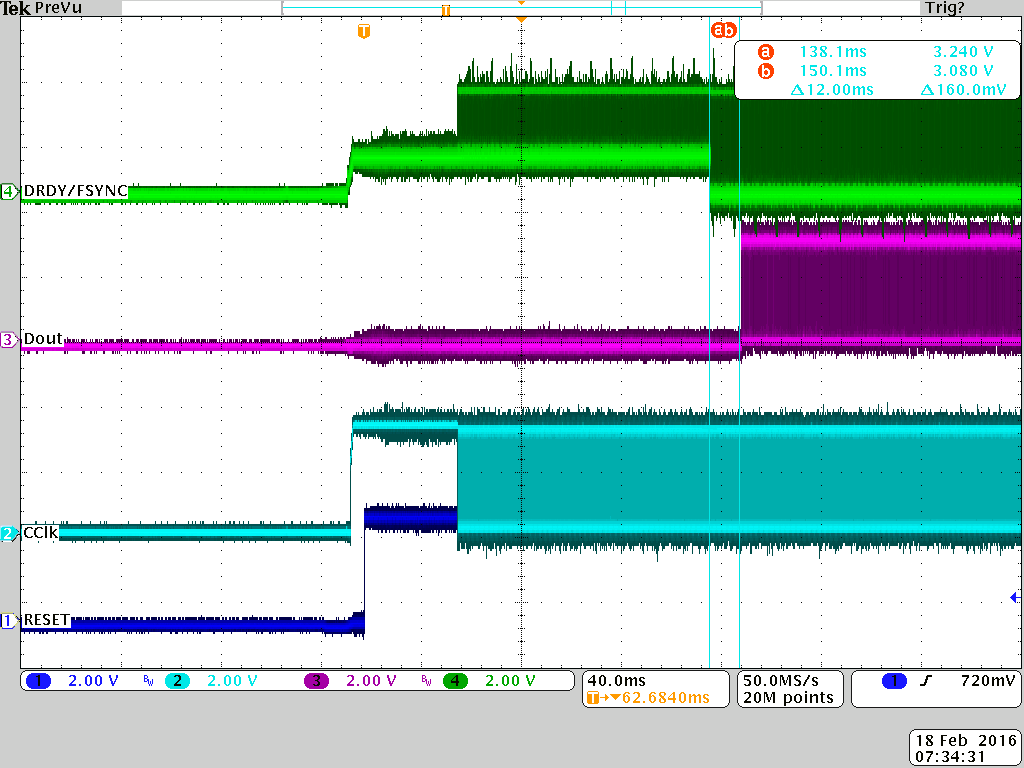

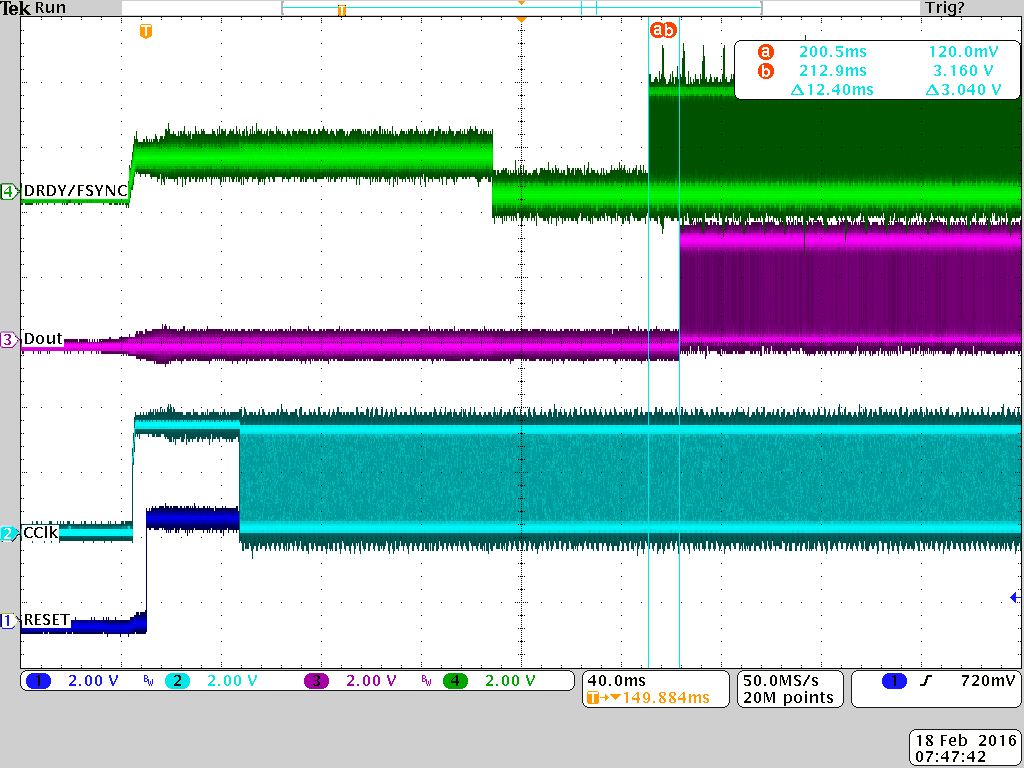

The capture below shows the FSYNC signal not dropping below ~1.2V during start-up. This is the reason I believe the DRDY signal is active.