Hi Everybody,

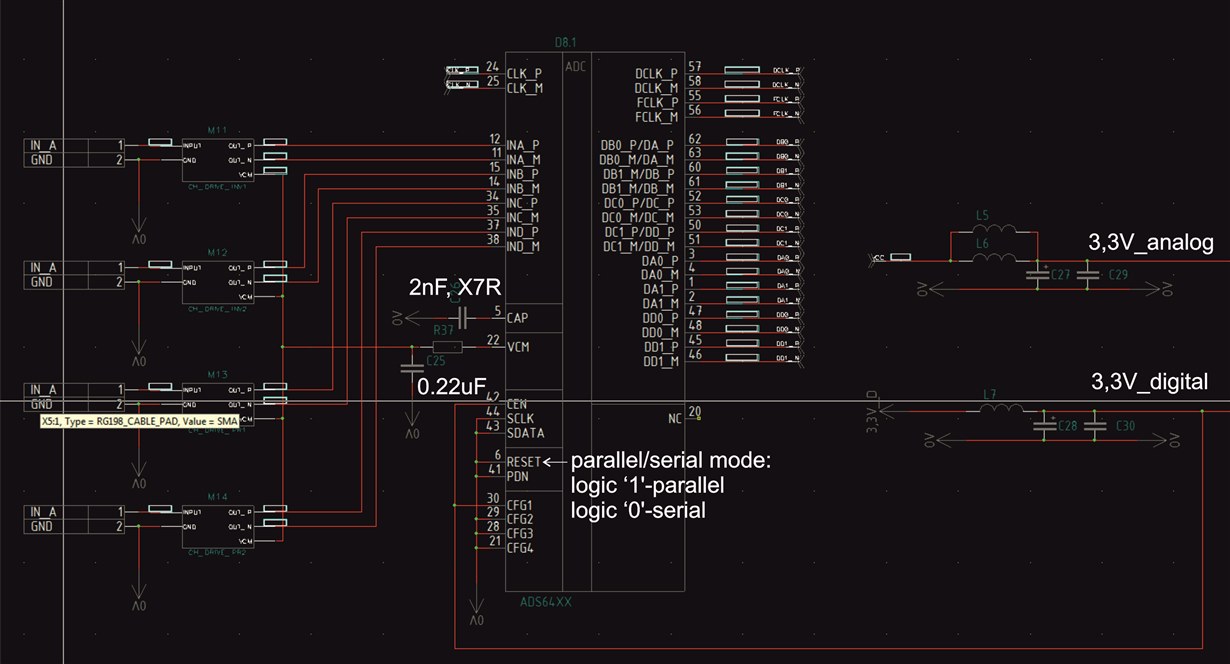

We have an issue with ADS6422 AD converter. The issue is the following. Sometimes without clear logic the PLL inside the ADS6422 can't sturt up correctly. There are 2 cases. The first is we have not nothing at the clk output, the second case is we have pulses at the clk output, but it similar if PLL can't locked. The ADS6422 have the pin, which is connected to external capasitor - 2nf according to the datasheet. There is nothing else about this capasitor in the datasheet.

We have the following statistic.

Totally 28 pcs tested at the temperature range (-40- +55):

- 1 pc - did not start up with nothing at the clk output at the temperature less -30C.

- 1 pc - did not sturt up with not locked PLL clk pulses at the output at the temperature less -15C.

- 2 pcs - first switch on did not start up with not locked PLL clk pulses or/and nothing at the clk output at the temperature less -30C

Totally 63 pcs tested at the normal temperature range (+10 - 25):

- 6 pcs - first switch on did not start up with not locked PLL clk pulses or/and nothing at the clk output at the normal temperature

We need your support with this issue. Have you any recomendation to choose the PLL capasitor. Maybe any other restriction or application notes for ADS6422 regarding our issue.

We use parallel programming in the both mode(serial/parallel programming option according to the datasheet). After the powering on the IC start up with parallel programming set after that we do not use serial programing and don't reset internal registers.

Hope for your prompt reply and support. Thanks in advance.