Hi Team,

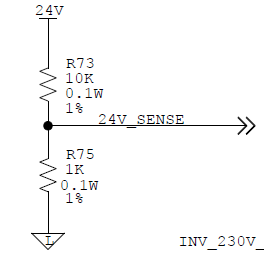

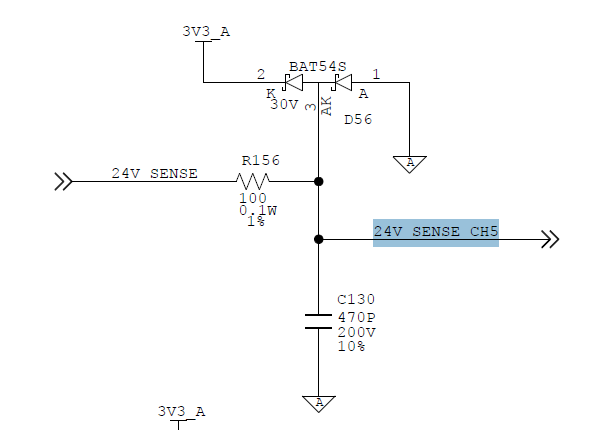

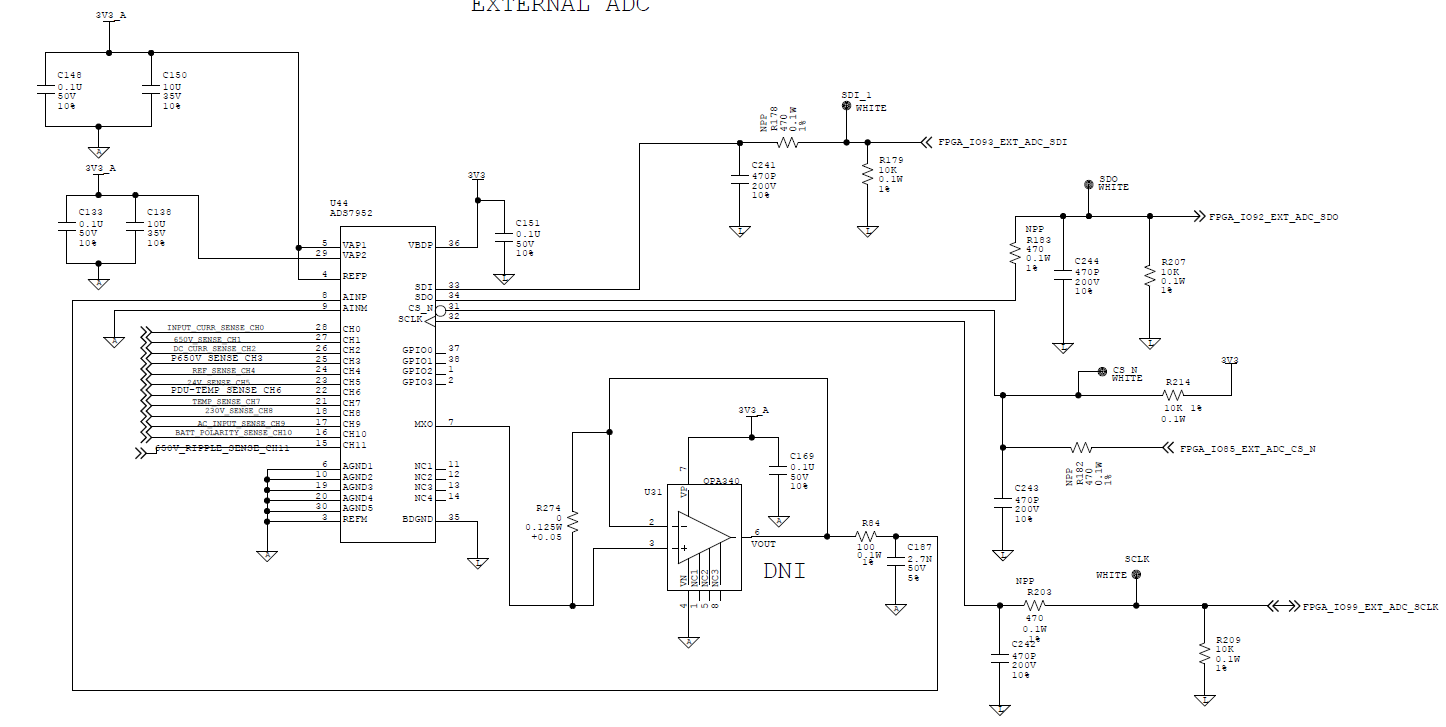

We are experiencing a ADC sense 100R resistor failure to open some times. To understand more in details please find the attached circuit below. 24V supply is getting reduced and get filtered with RC ( 100R and 470pF) and given to the external ADC.

Q1: we have seen sometimes the series resistance 100R is failing. Please let us know whether we need to change the resistor to higher value. or do you see any other reason of failure.

Q2: 470pF capacitor can I increased to 100nF to 470nF for better filtering the signal; this is for other noisey signal I need to use bigger capacitor

Q3: Output of the ADS7952 is going to the FPGA (10M25SAE144C8G) for ADC sensing. we have seen one time Three line going to the FPGA Pin has failed short. (refer 3rd circuit for details). I mean SDI and SDO and CLK line. Please suggest whether any circuit modification is needed to avoid the failure.

Let me know if you need any more information.