Hello,

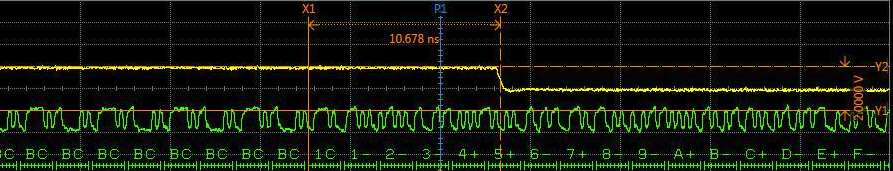

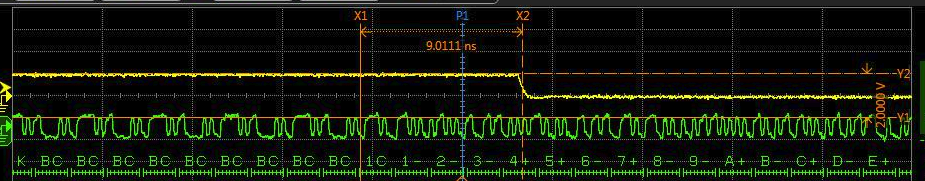

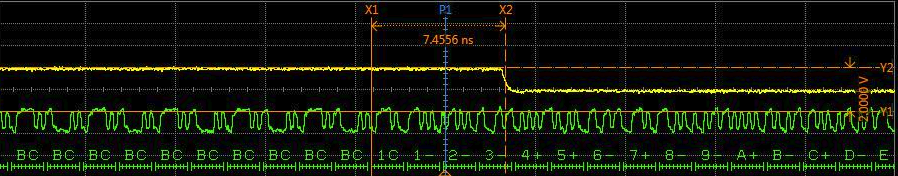

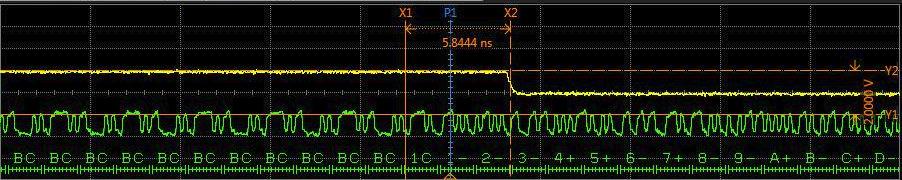

I'm currently working on a JESD204B core implementation on an FPGA interfacing a DAC37J82. Clocking and SYSREF to both devices is provided via AD9528. While establishing the link and sending data is not a problem, but we can't achieve deterministic latency between FPGA and DAC37J82. The figure 1~4 show the latency between sysref positive edge to the ILA start K code /R/ ( 1C) vary when a new JESD link is set up . Which means latency between FPGA and DAC37J82 is not deterministic.

figure 1

figure 2

figure 3

figure 4

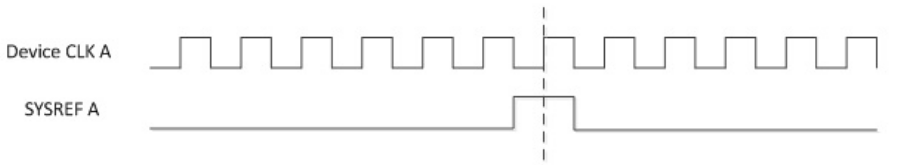

1. the sysref and dacclk phase relation just as figure 5 , dacclk is 125m and sysref pulse width is 160ns .

2. Program config36 (0x24) = 0x30 => clock divider use sysref skip one pulse and then use next .

3. Program config92 (0x5c) = 0x0005 => use skip two pulses and then use next. Ignore Link1, Link2, and

Link3 since they are not used.

4. the RBD pushed to the maximum 32 .

Is there anything am I missing?