dear sir

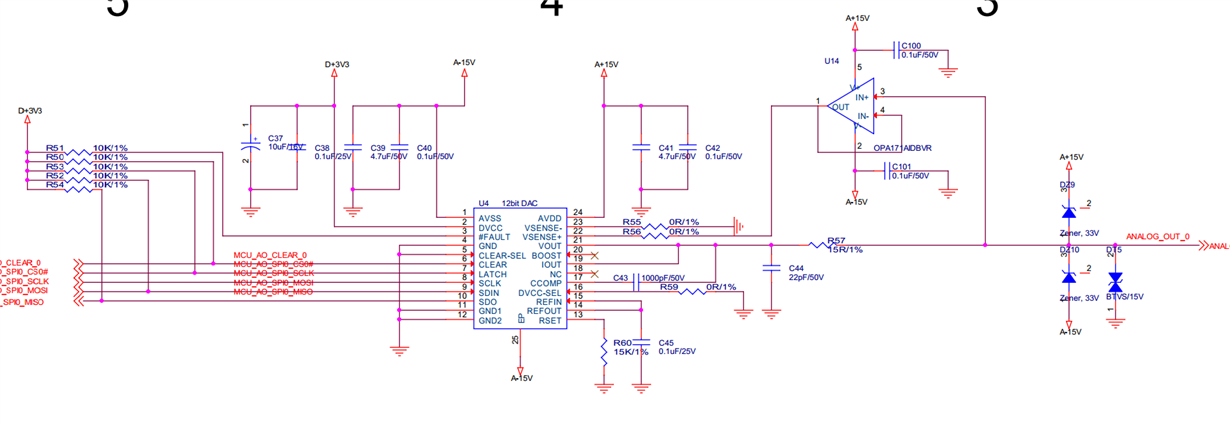

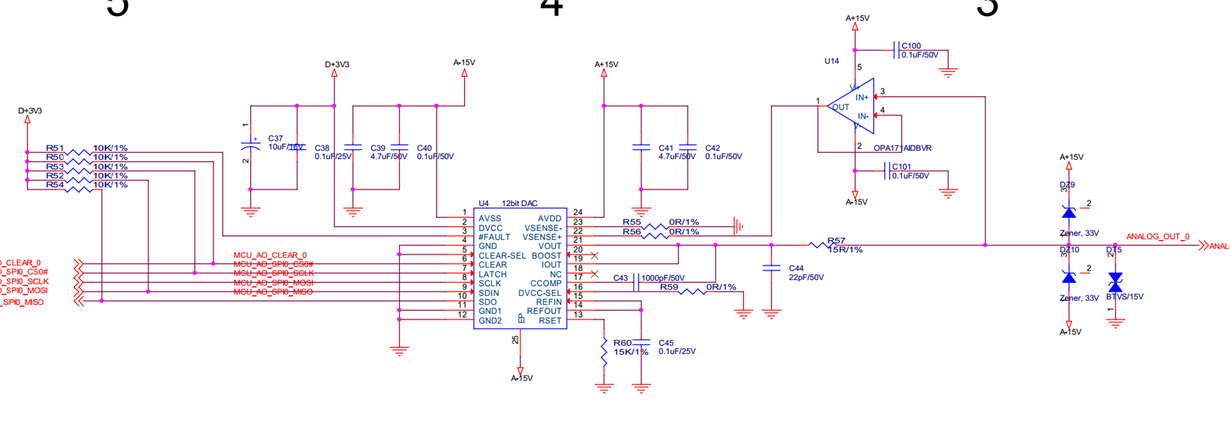

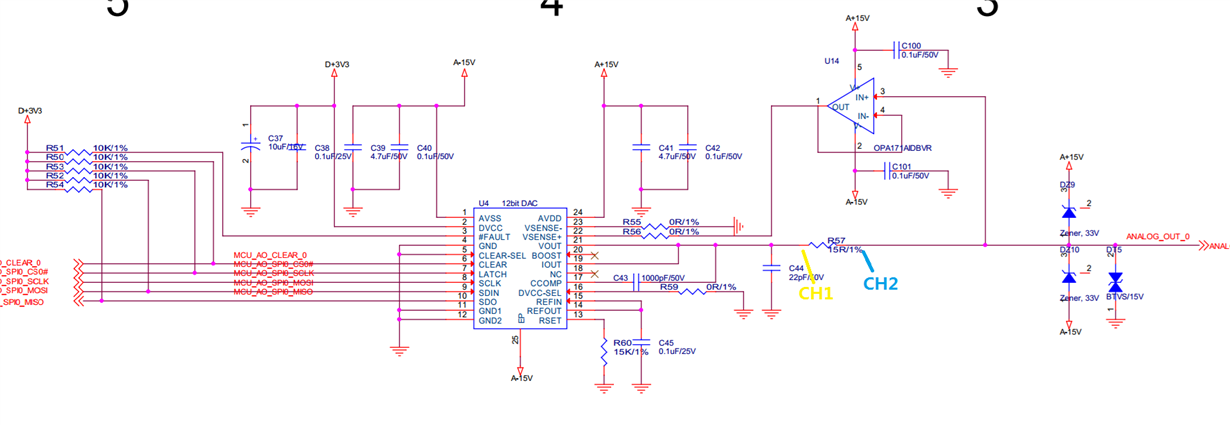

We control the DAC7760 output voltage or current through the SPI interface, and then measure the voltage or current using a multimeter, directly connected to the connector.

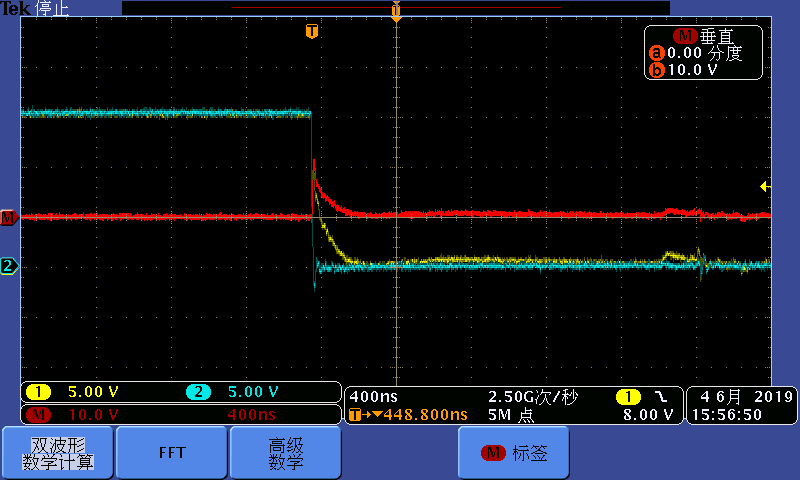

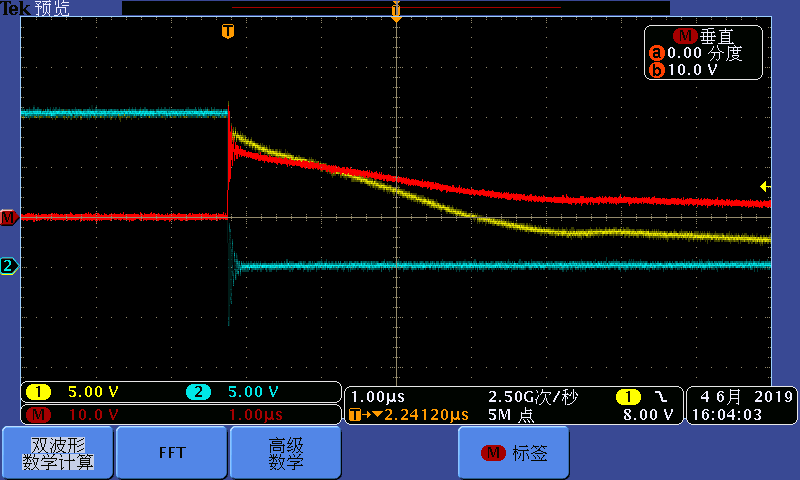

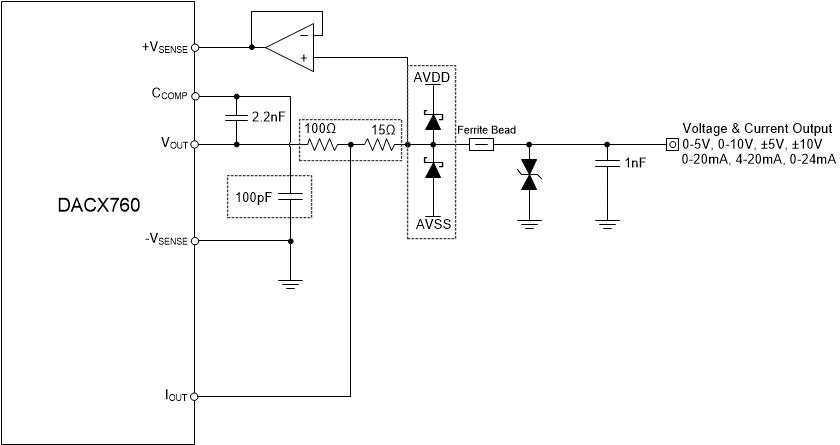

In this process,we found short circuit between the power supply of DAC chip and GND,there is a R3 between AVDD and Boost, we put a 15 ohms in the output current to

limit the current , but when IOUT connect to GND, the DAC7760 damage, do we have a short circuit protection ? what`s the proper load resistance ?