Other Parts Discussed in Thread: LMK01000, DAC3482

Hi,

I am running DAC3482 from my own board. An xilinx K7 FPGA is used to drive DAC through LVDS and controll onboard DDR memory. An external 1228.8MHz clock source is applied to LMK01000 then distributed to DAC and FPGA.

DAC CLK = 1228.8MHz

Interpolation = x4

16 bit Data Mode

2's Component Disabled [data range 0 ~ 65535]

DAC IF freq = DAC CLK/16 = 76.805MHz

DAC was configured by MSP430 MCU as below:

DAC3482_RST_LOW;

delay_ms(10);

DAC3482_RST_HIGH;

DAC3482_TXEN_LOW;

unsigned int cfg2 = 0;

if(Dac3482_Twos) cfg2|= BIT1;//2's disabled

//if(Dac3482_xIF) cfg2|= BIT4;

Dac3482WriteSpi(0x0280D0 | cfg2);

unsigned int cfg0 = Dac3482_xINT>>1;//Dac3482_xINT = 4

cfg0 = cfg0 <<8;

cfg0 = cfg0 + 0x1C + BIT7;

Dac3482WriteSpi(cfg0); //Reg 00

Dac3482WriteSpi(0x01020E); //Reg 01

Dac3482WriteSpi(0x03A000); //Reg 03

Dac3482WriteSpi(0x103000); //Reg 10

Dac3482WriteSpi(0x140000); //Reg 14 - 15:0

unsigned long cfg15 = 0x150000;

if(Dac3482_xIF>1)

cfg15 = cfg15 + 0x10000/Dac3482_xIF;//Dac3482_xIF = 16

Dac3482WriteSpi(cfg15); //Reg 15 - 31:16

Dac3482WriteSpi(0x1B0800); //Reg 1B

Dac3482WriteSpi(0x1F8180); //Reg 1F

Dac3482WriteSpi(0x202201); //Reg 20

//Frame

//FPGA RST

FPGA_RST_LOW;

delay_ms(100);//apply Frame

Dac3482WriteSpi(0x050000); //Reg 5

Dac3482WriteSpi(0x1F818A); //Reg 1F

Dac3482WriteSpi(cfg0); //Reg 0

Dac3482WriteSpi(0x1F8188); //Reg 1F

Dac3482WriteSpi(0x200001); //Reg 20

delay_ms(100);

DAC3482_TXEN_HIGH;

Here are some test data,

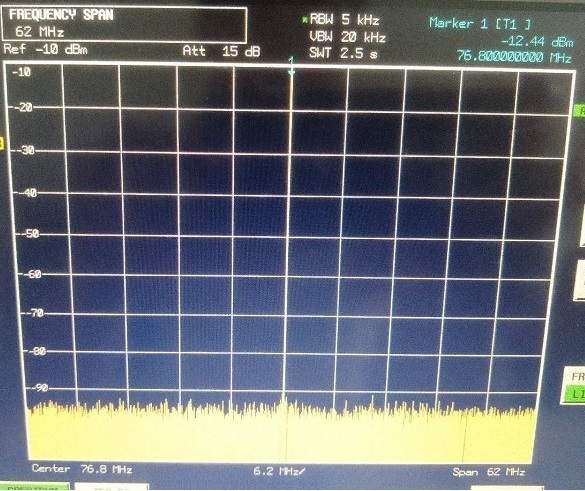

DAC IF Output (no iq data)

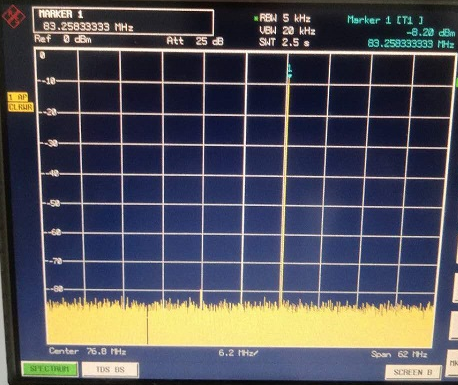

play a 48-point-sine wave (data file contains 819200 cycles)

data frequency = dac clk / 48 / 4 = 6.4MHz; Output freq = 76.805 + 6.4 = 83.205M

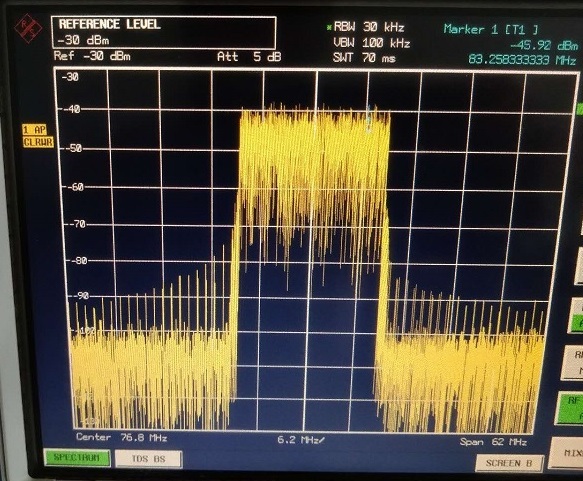

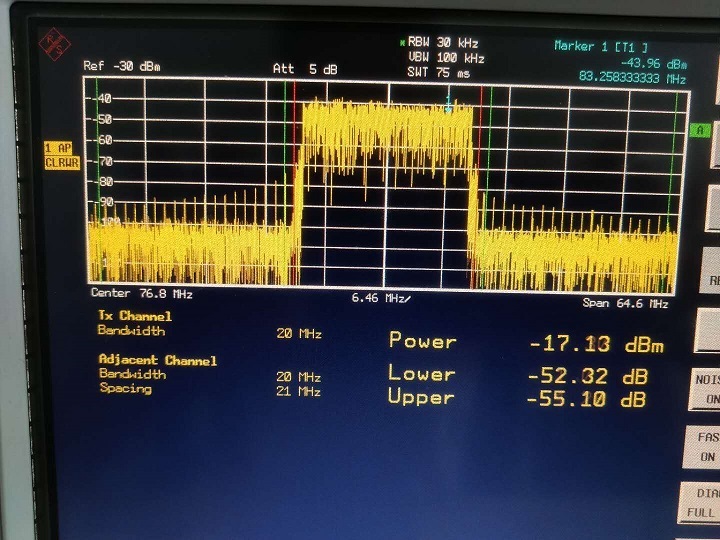

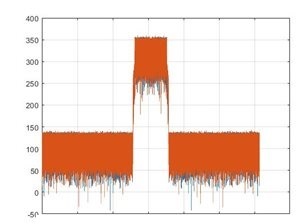

play 20M LTE waveform( 307.2M sample rate)

The LTE waveform data file spectrum is clean in Matlab; the data file is also verified by HSDC+TSW1400+TSW3085. So waveform file cann't be the reason.

I don't understand why threre so may spurs when playing the modulation data while everything is ok with sine wave.

Is there anybody can help to remove those spurs?

Any idea will be highly appreciated.

Thanks in Advance!

TL