Dear team,

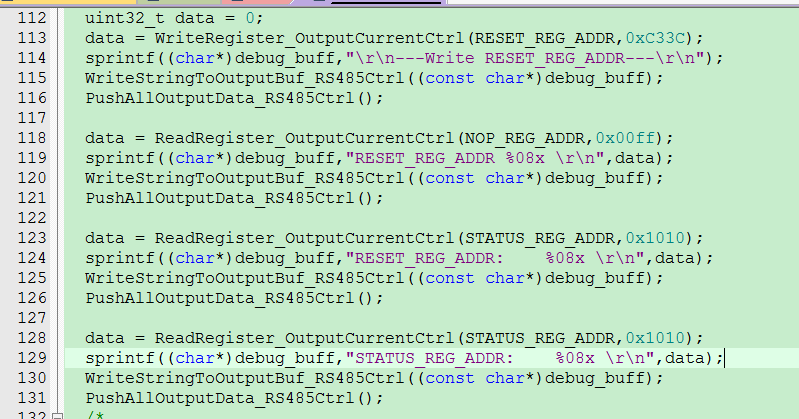

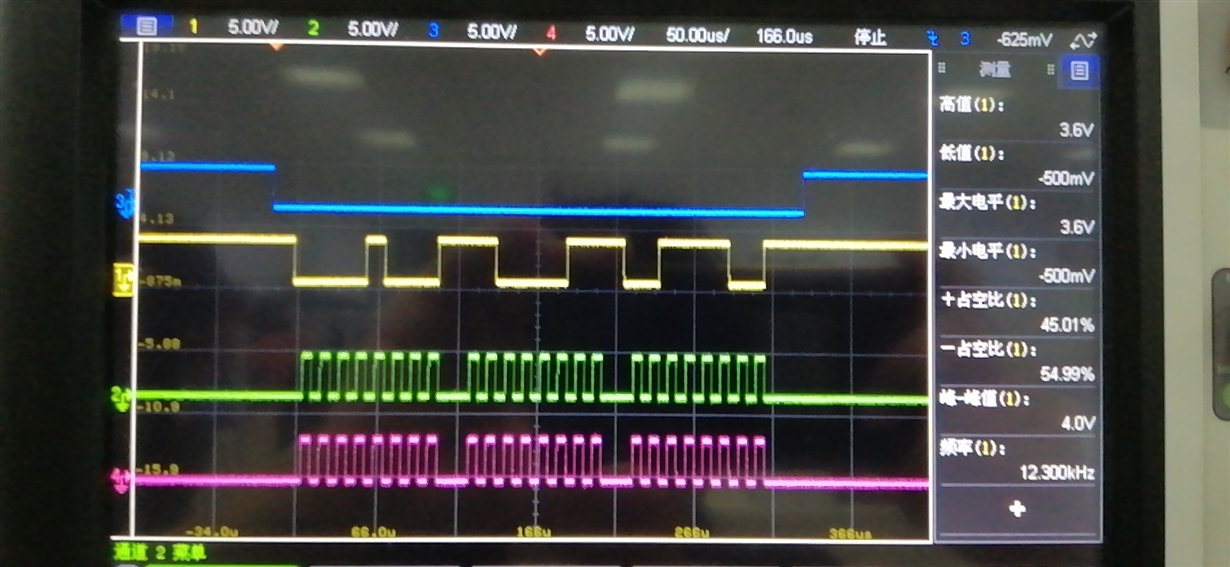

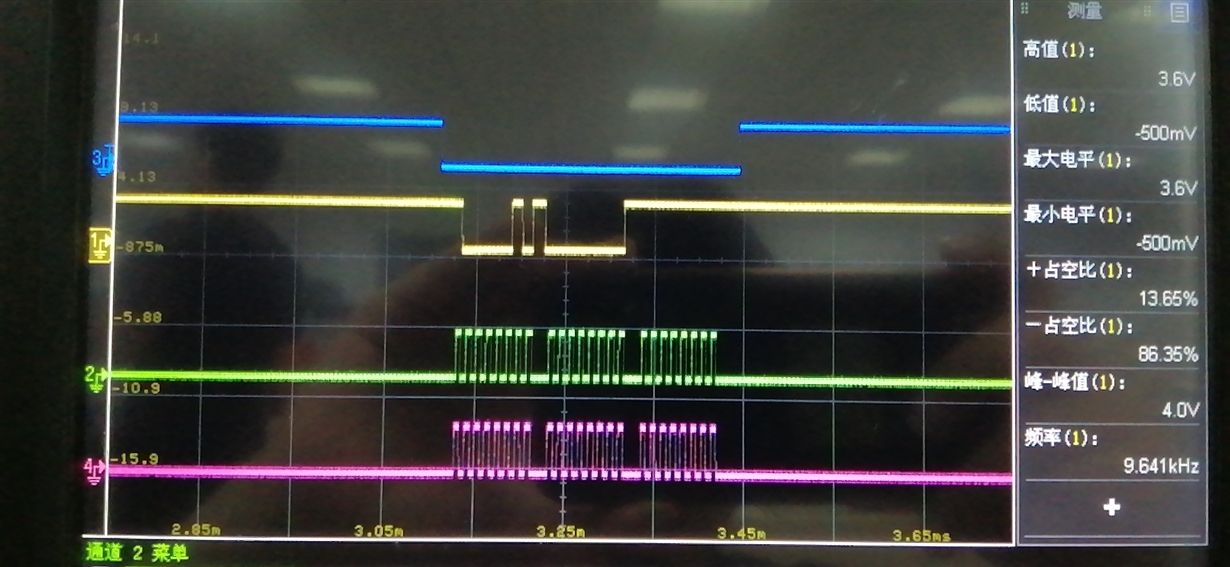

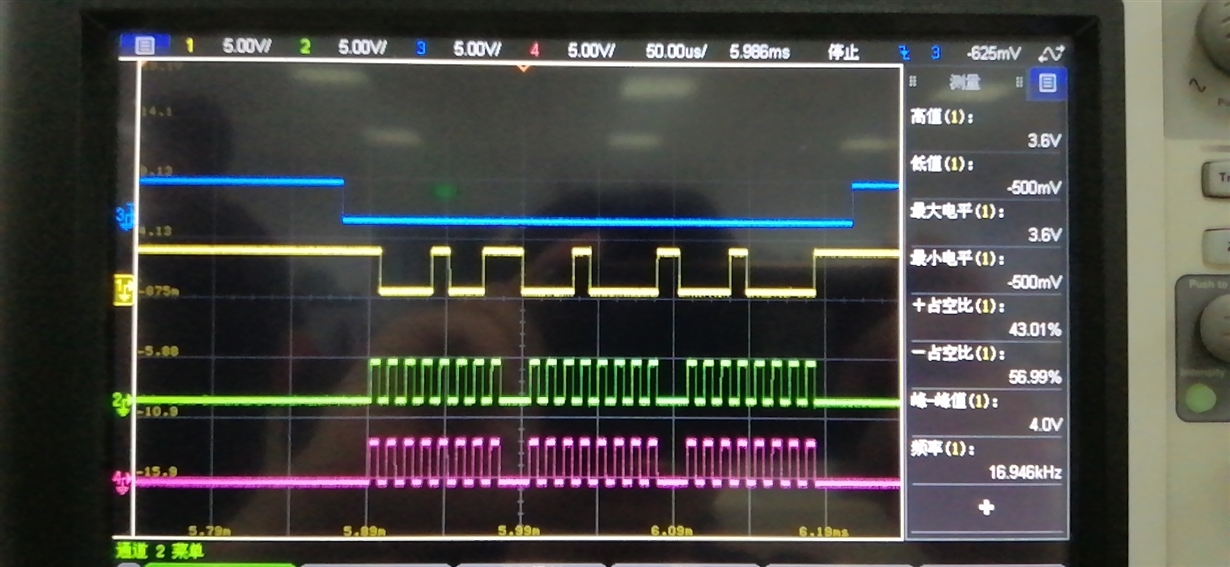

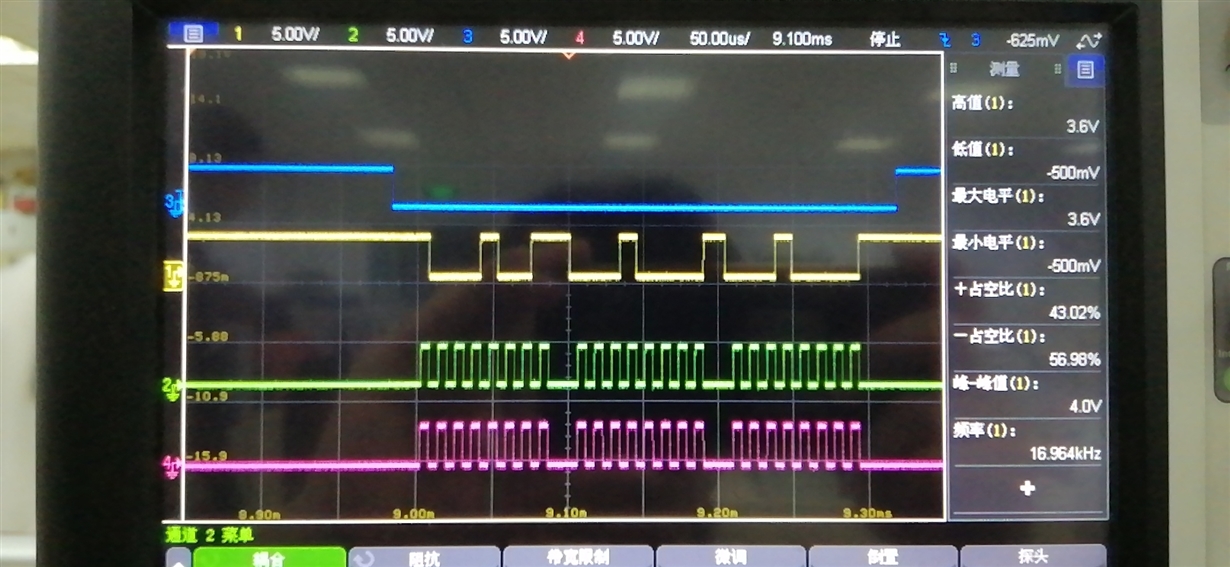

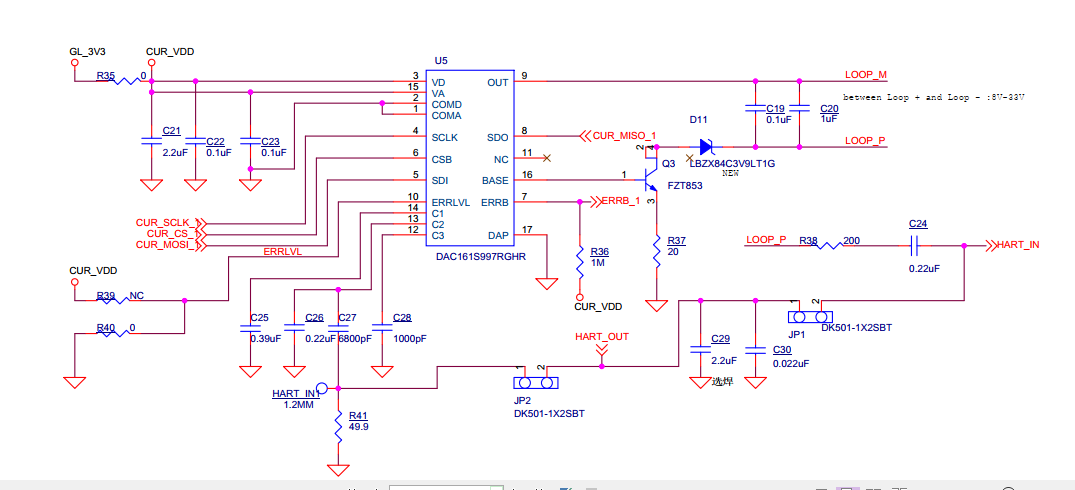

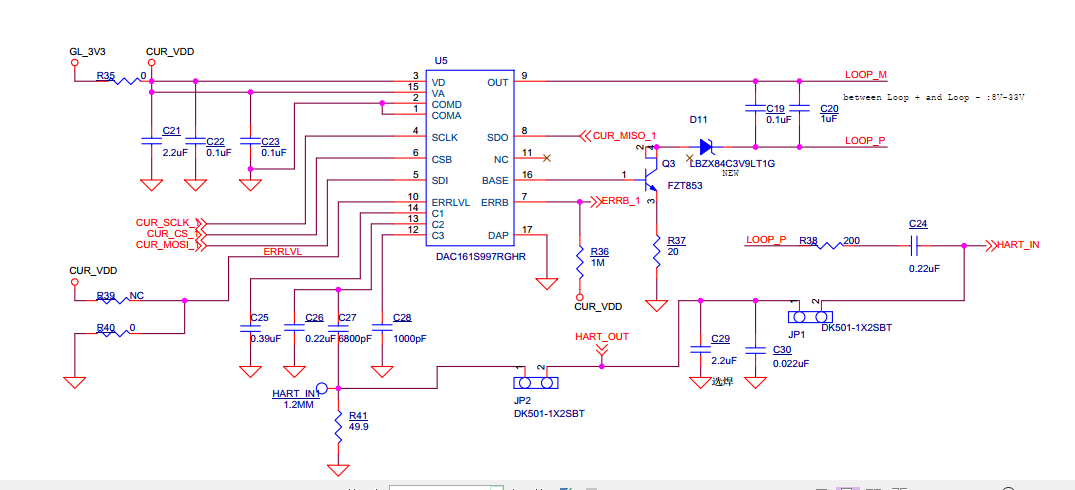

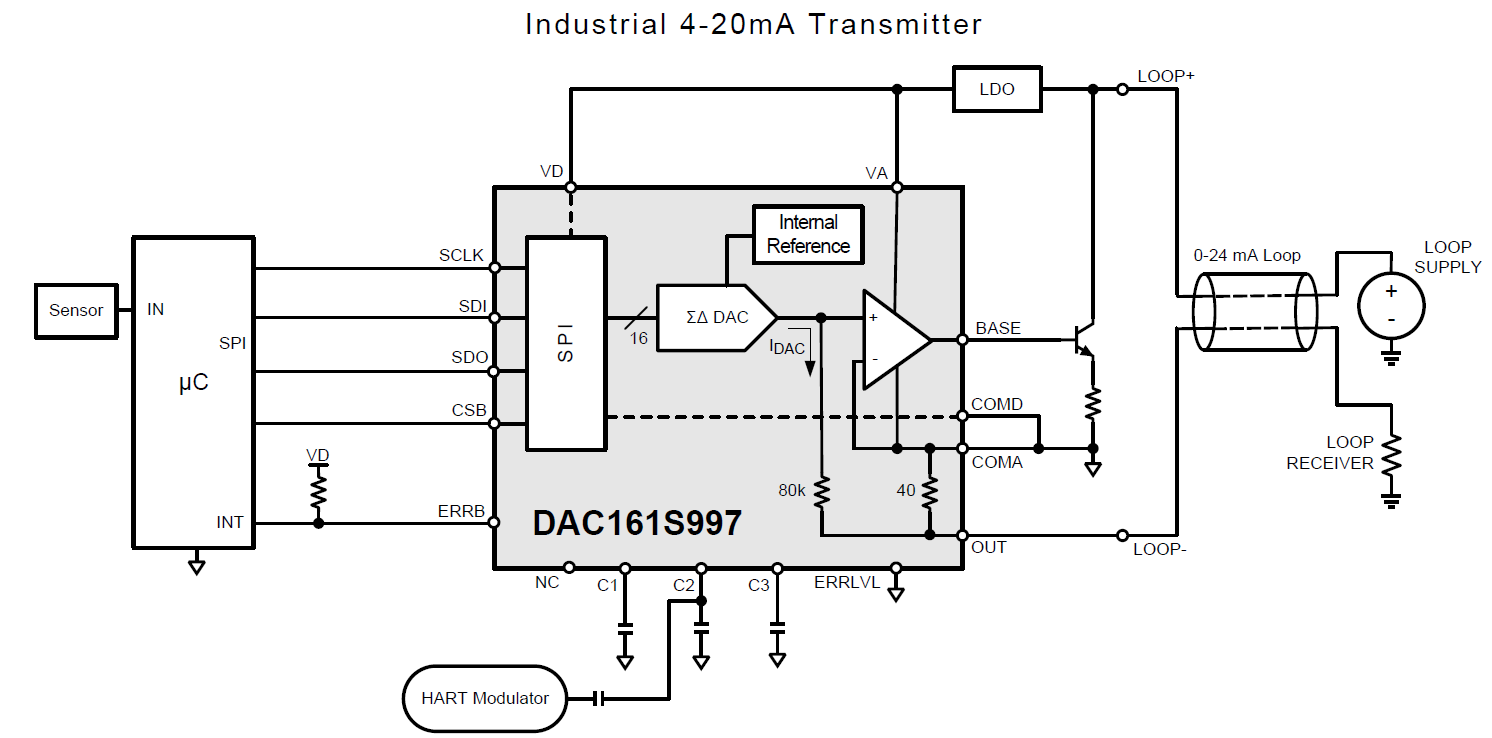

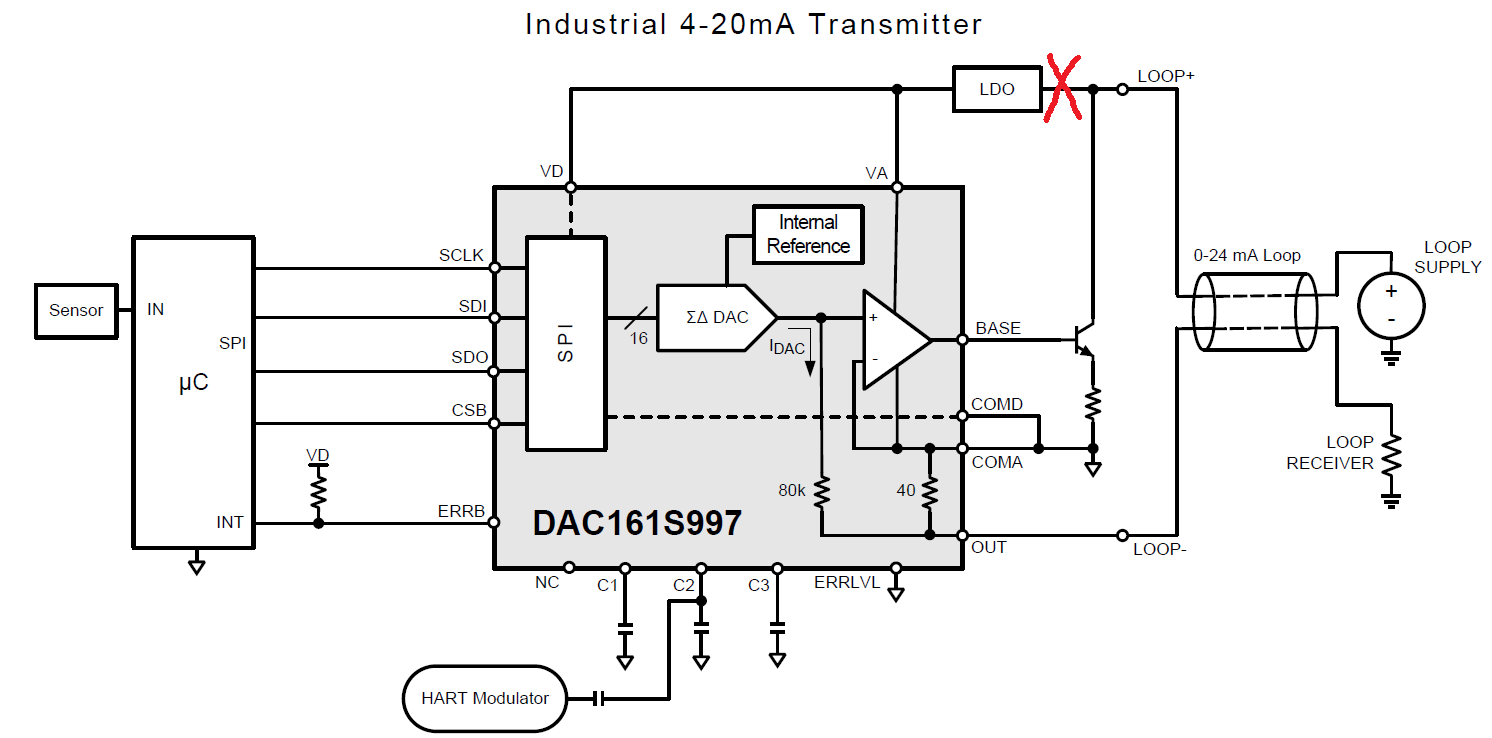

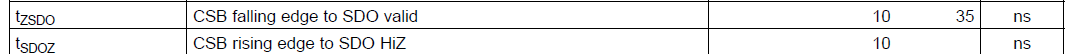

Below the first picture is the programming. One Write command, and three read command. And the CSB(blue), SDI(yellow), SDO(green), SCLK(pink) waveforms are as following. We can see that, the SDO still has no change. Could you please tel me the reason? The schematic is as below. In addition, about the timing requirement, in our datasheet the tZSDO(CSB falling edge to SDO valid) should be smaller than 35ns, but the cusomer's MCU can't meet this requirement. Is this fault related to the timing requirement?

Thanks & Best Regards,

Sherry