Part Number: TSW40RF82EVM

Hello,

Is it possible to make a new configuration for TSW40RF82 EVM board with only 1 input and 1 output.

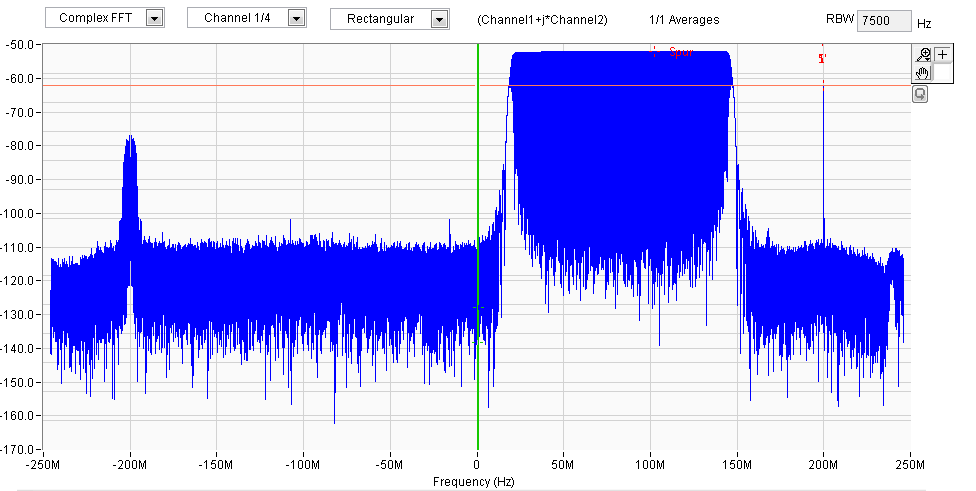

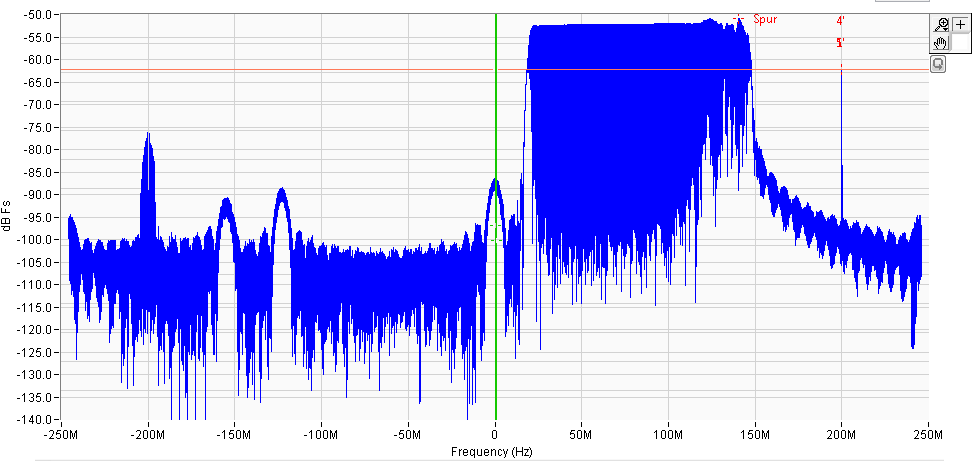

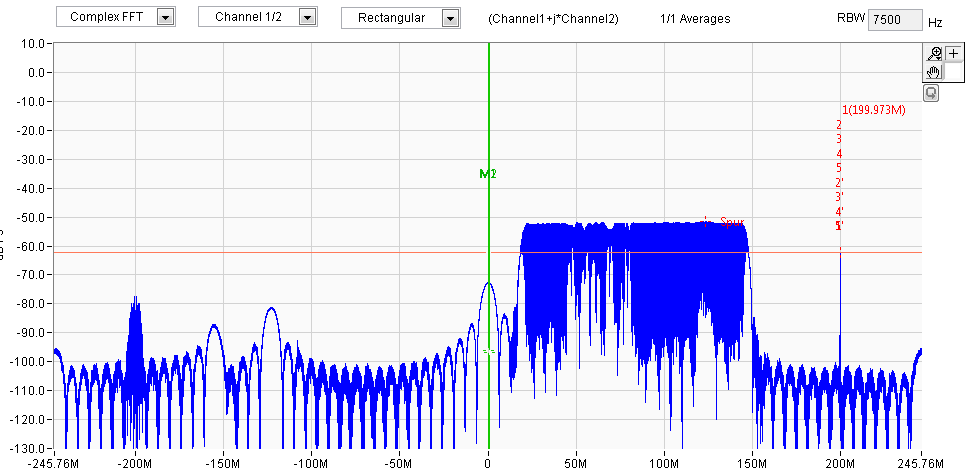

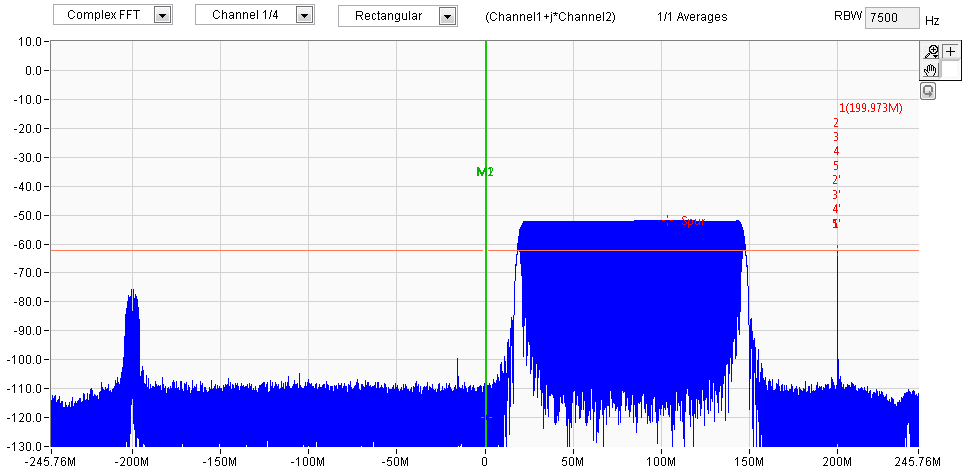

Currently I use 2T2R2T2R_RevC_ConstInput_6xDec_12xInt_2949p12M_5898p2_4915p2Gb and i would like same configuration but more like 1T1R_RevC_ConstInput_6xDec_12xInt_2949p12M_5898p2_4915p2Gb.

Regards,

Damien