Other Parts Discussed in Thread: ADS8353

Hi team,

My customer considers to use ADS8325IB and provided some questions.

- DOUT becomes low after power up and it keeps low even after CS asserted.

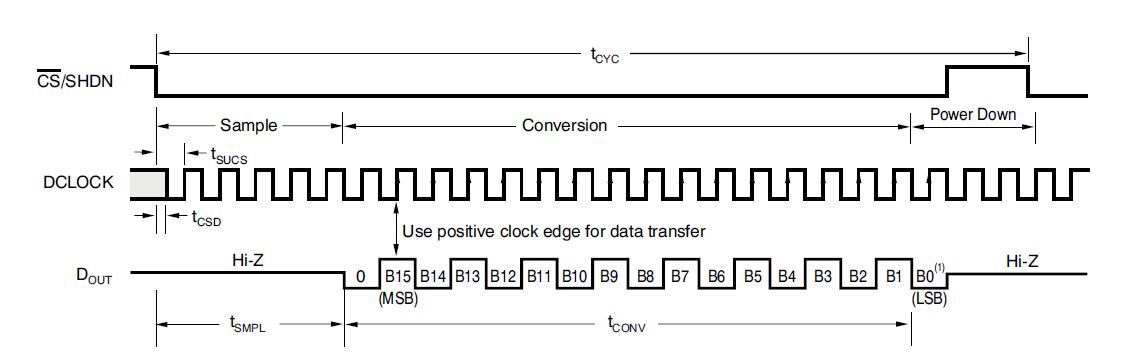

Is there possibility that ADS8325 broken? - Timing Chart shows that max TCSD is 0ns.

Does it mean DCLOCK needs to be low before CS becomes low?

If this timing is violated, will communication error occur?

Best regards,

Shota Mago