Part Number: DAC81408

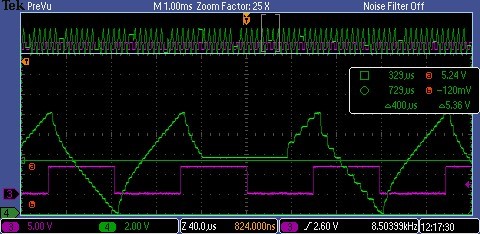

I have a design that uses the first 4 channels as arbitrary waveform generators running at a 400Khz update rate (at 50Mhz SPI) and then synchronously updating them. The four remaining DACs are used as utility DACs that can be updated at any time. My RTL design uses the streaming mode for the first 4 channels then tacks the channel update for one of the 4 utility dacks after the streaming of the first 4 DACs. However, after streaming DACS 1-4, then issuing an LDACn strobe, I run into issues if the next DAC is DAC5. the other 3 work fine. Is there a timing relation sip between the LDACn and selecting the next sequential DAC after the streaming selection?

Again, my sequence is:

1) CS low

2) 72 bits transferred - DAC1_ADDR (8bits), DAC1_DATA(16bits), DAC3_DATA(16bits), DAC3_DATA(16bits), DAC4_DATA(16bits)

3) CS high

4) 20nS delay

5) LDACn Strobe for 20nS

6) 15nS delay

7) CSn low