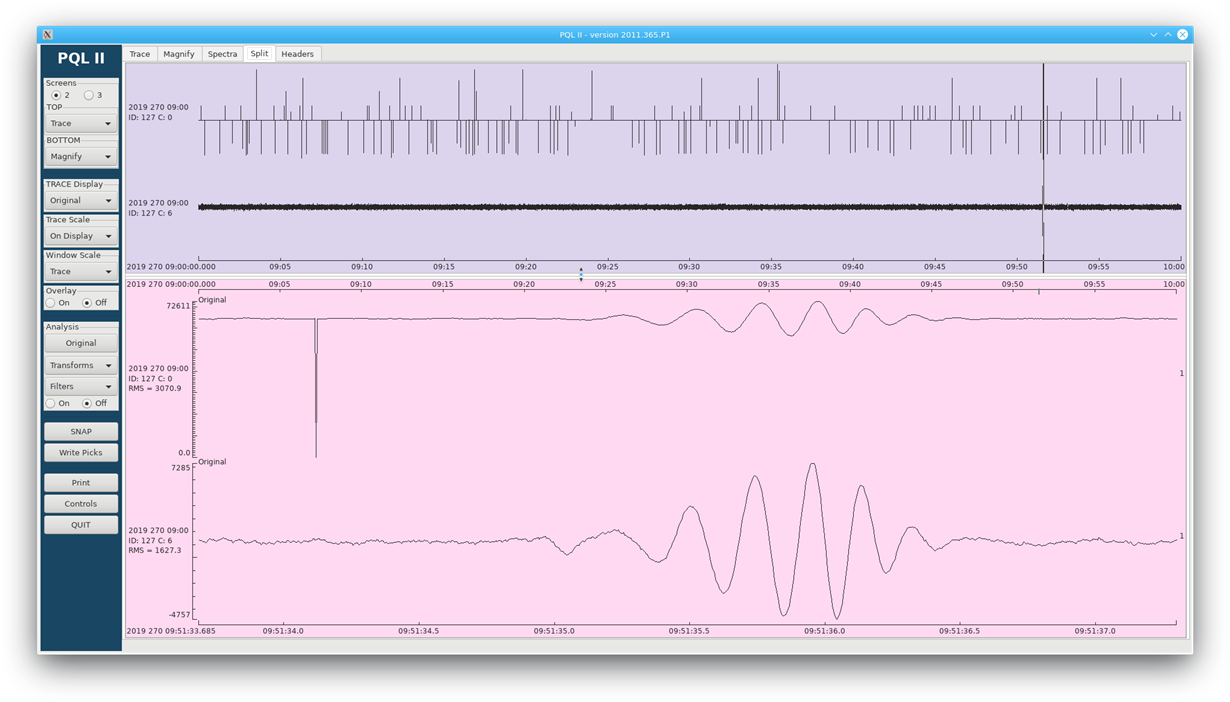

I am designing a data logger for geophysical applications using the ADS1282. I already build several prototype boards for lab and field testing. The initial field test showed a considerable amount of noise as shown in the attached figures. The top half of the figure (with title PQLII) shows an overview of data recorded by the prototype logger (top trace) and an old logger using a Cirrus Logic ADC (bottom trace) . The sensor connected to both data loggers is a vertical geophone. The bottom half shows an event detected by the sensors. The recorded signal by the ADS1282 logger is as expected and comparable to the signal recorded by the old logger. However, this figure also shows that the prototype logger is noisy. Several voltage spikes can be observed in the overview trace at the top of the figure. As can be seen from the second trace, the old logger is free of this noise. The data was collected on the field and both loggers were deployed in the same area, thus eliminating the environment as the source of the noise. The both the prototype and old loggers use the same MCU and the same power regulators. Have you seen noise like this in any other design using the ADS1282? Could noise like this be caused by errors in reading data from the ADCs?

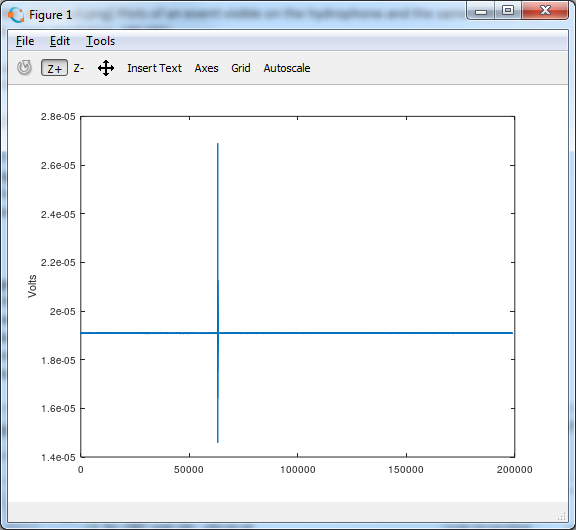

The other figure (Figure 1) shows data recorded when the input to the ADS1282 is connected to the internal 400 Ohm resistors. In this a single instance of a large voltage spike is observed. In general, data recorded in lab tests still show this noise albeit with a lower number of occurrences than in the field test. Any suggestions about what may be the source of this noise. So far I have tried, shielding the ADC board from the MCU and Power boards and the noise is still present.

Thank you.

Best regards,

Alex