Hi all,

I'm trying to develop an algorithm on FPGA to process the sampled data by the ADC. We're using TI's ADC12J1600 and Xilinx's KC705, also TI's TSW14J10 for connecting the two boards.

Here's the configuration of the ADC:

Decimation = 4;

LMFS = 4222;

K = 16;

Reference Clock = 200Mhz;

Device Clock = 100Mhz;

Here's the output data format:

I've created a 4-lane JESD204B RX project based on Xilinx's JESD204 Hardware Demo and JESD204 Example Design, here's the schematic:

The configuration of the RX core is matched to the set up of the ADC. I chose to include the shared logic in the core considering we have only one RX core in our project.

By using the VIO, we can correctly perform the register read/write access. Here's the AXI Control Register configuration:

0 => x"8008", -- Addr x008

1 => x"0000", -- Data x0000_0001 Enable Lane Alignment

2 => x"0001",

3 => x"800C", -- Addr x00C

4 => x"0000", -- Data x0000_0001 [0] Enable Scrambling

5 => x"0001",

6 => x"8020", -- Addr x020

7 => x"0000", -- Data x0000_0001 F (octets per frame) = 2

8 => x"0001",

9 => x"8024", -- Addr x024

10 => x"0000", -- Data x0000_000F K (Frames per multi) = 16

11 => x"000F",

I'm using GPIO LEDs to check the interface signal, here's the results:

LED[4] is blinking, showing the FPGA can receive the reference clock and global clock;

LED[3] is on, showing the system clock is locked, and generating 200MHz clock for AXI Controller;

LED[2] is on, showing the JESD204B receiver can generate RX_aresetn signal, which serves as the reset signal for data demapping block;

LED[1] is on, showing the tx_resync is asserted, which is sent out to ADC;

LED[0] is on, showing the rx_resync is asserted, which is the synchronizing signal generated by the receiver;

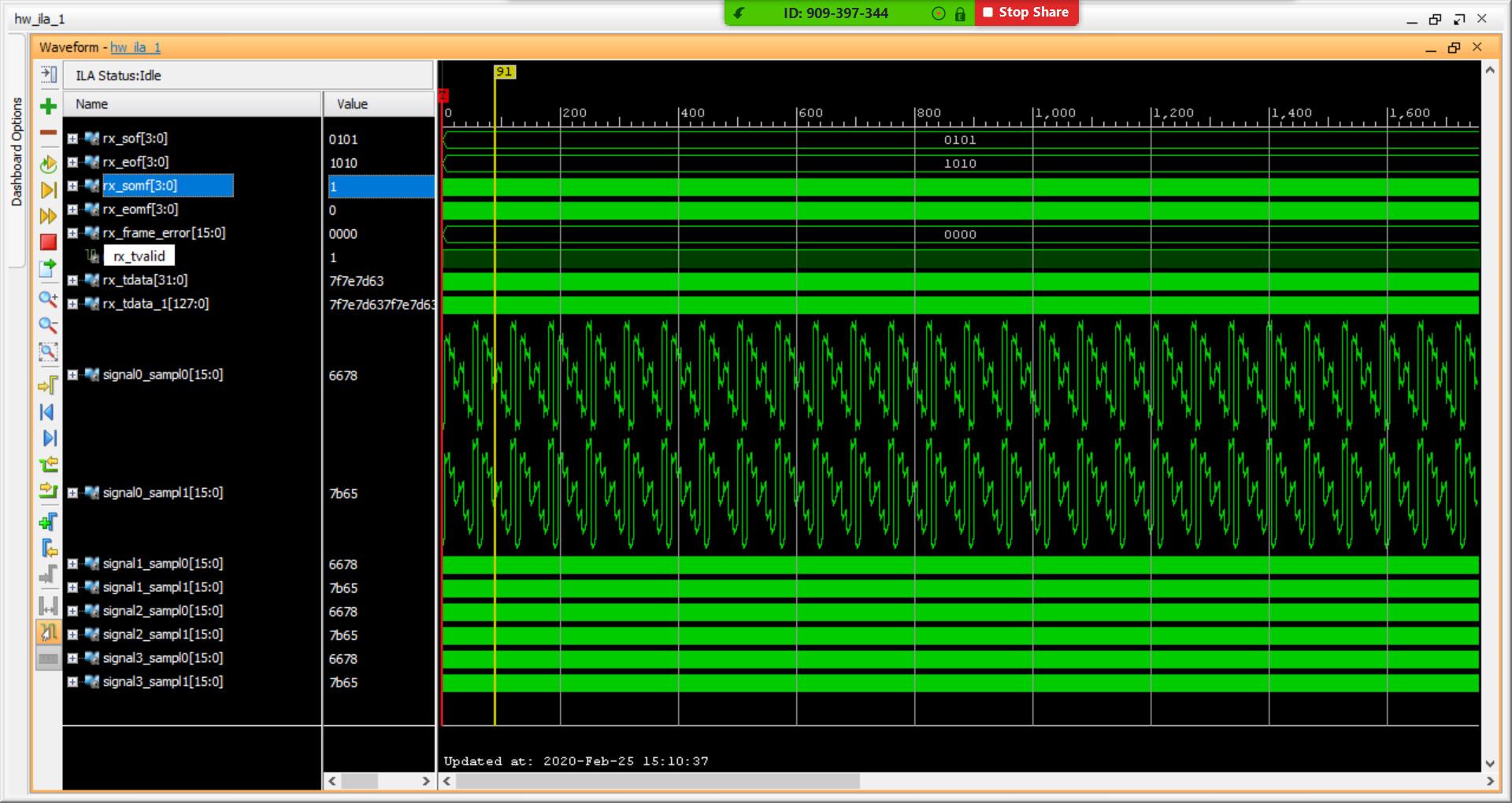

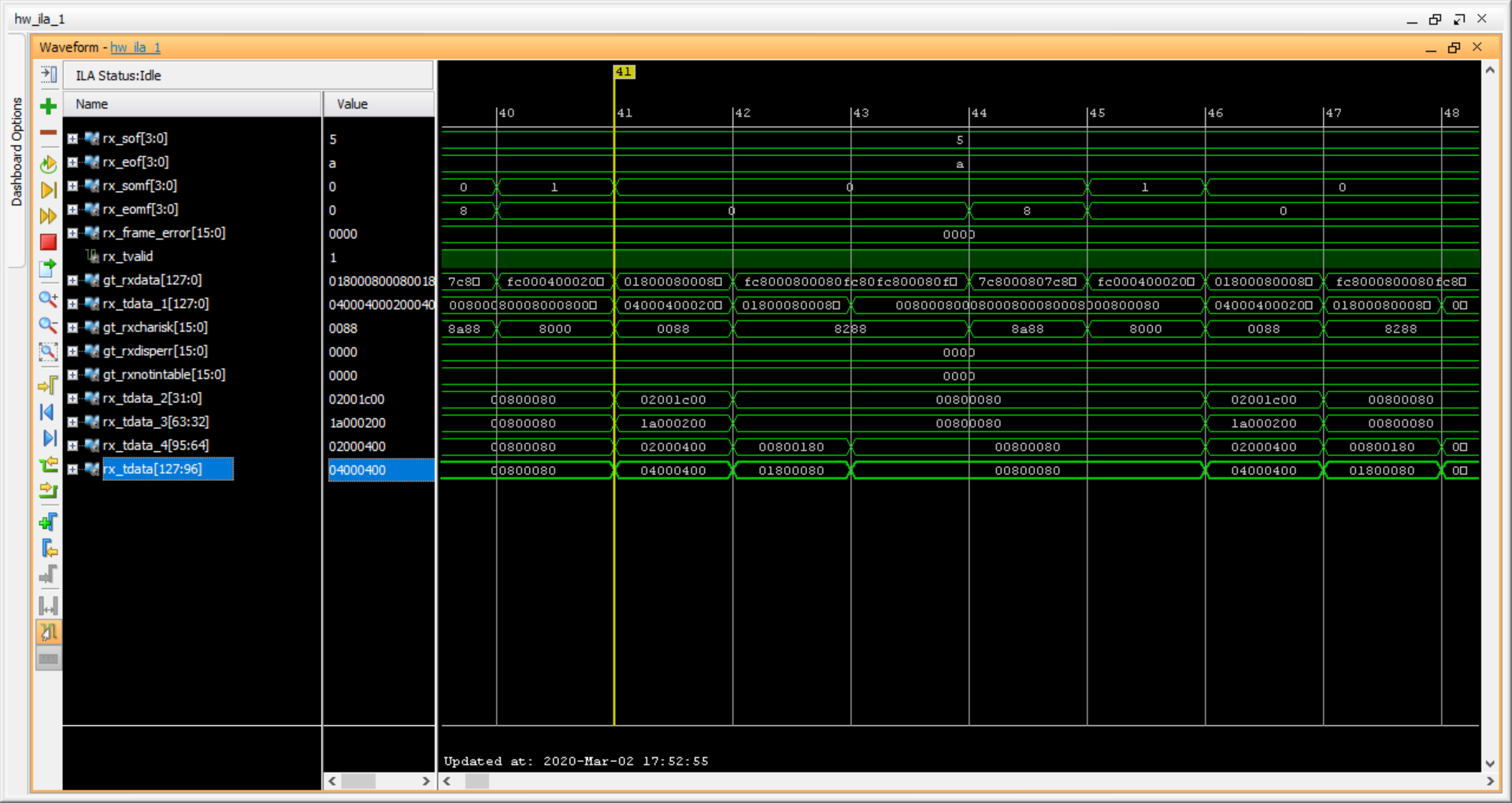

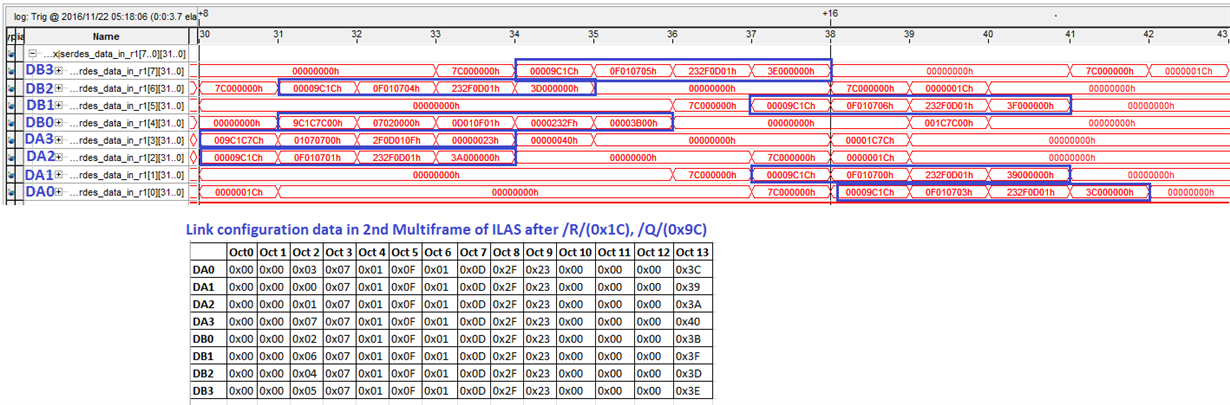

The data is captured by the ILA, we have set the ADC to Ramp test mode and normal, here's the result:

(1) Ramp test mode -- each lane transmits an identical octet stream that increments from 0x00 to 0xFF and repeats.

The data from 4 lanes are exactly the same, which is reasonable since the ADC is sending identical octet-stream to each lane. However, the value of the captured data is incorrect for now.

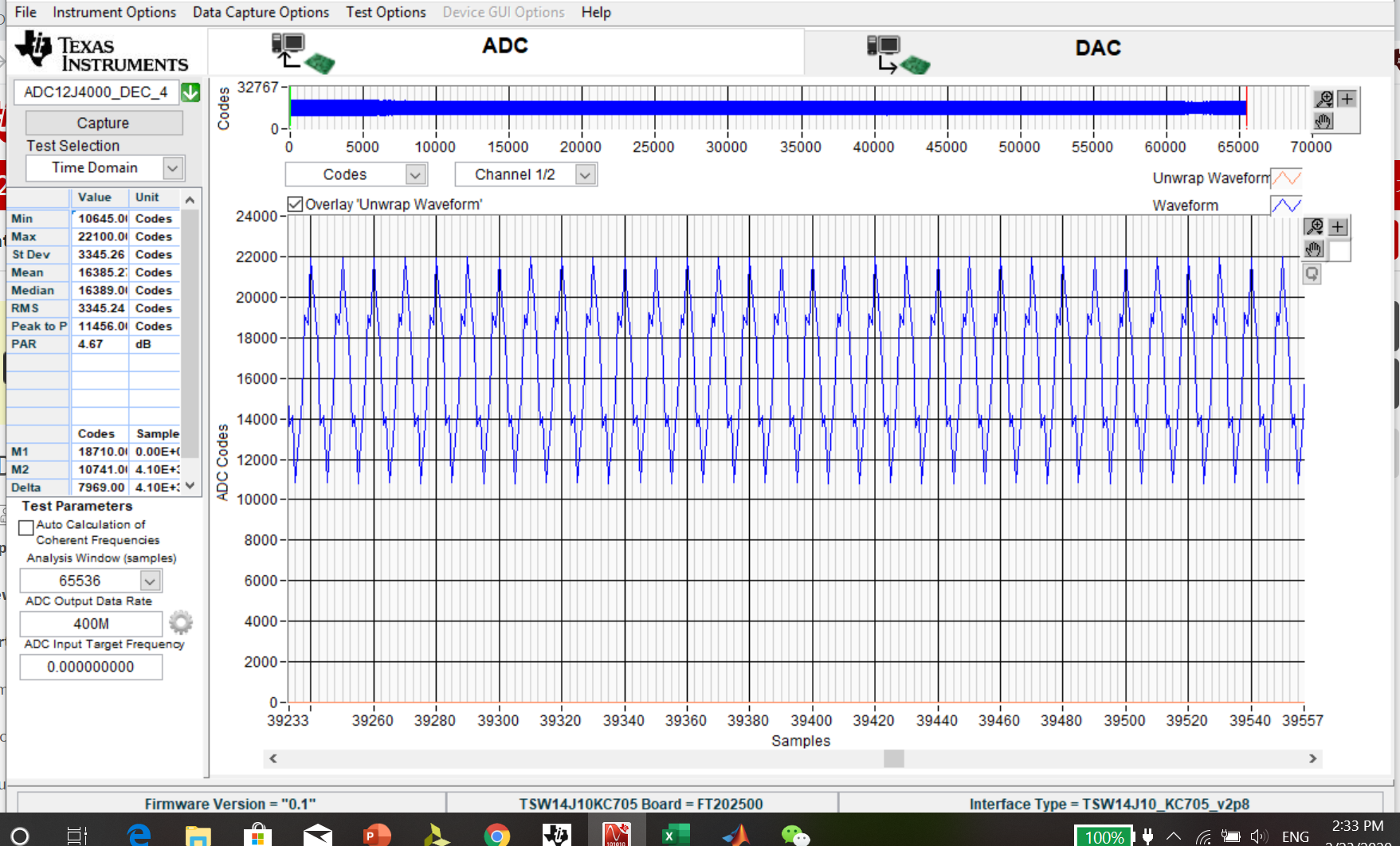

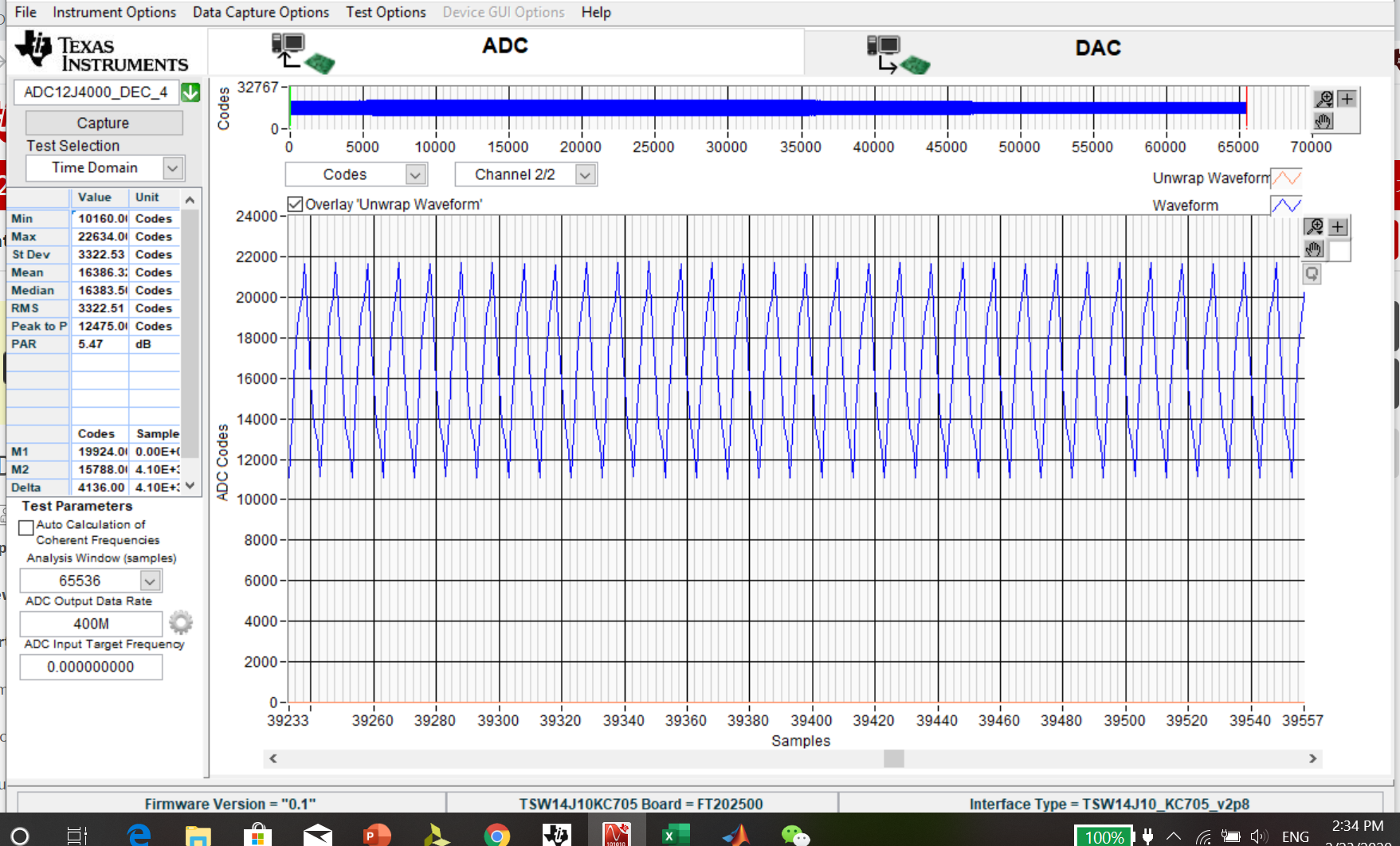

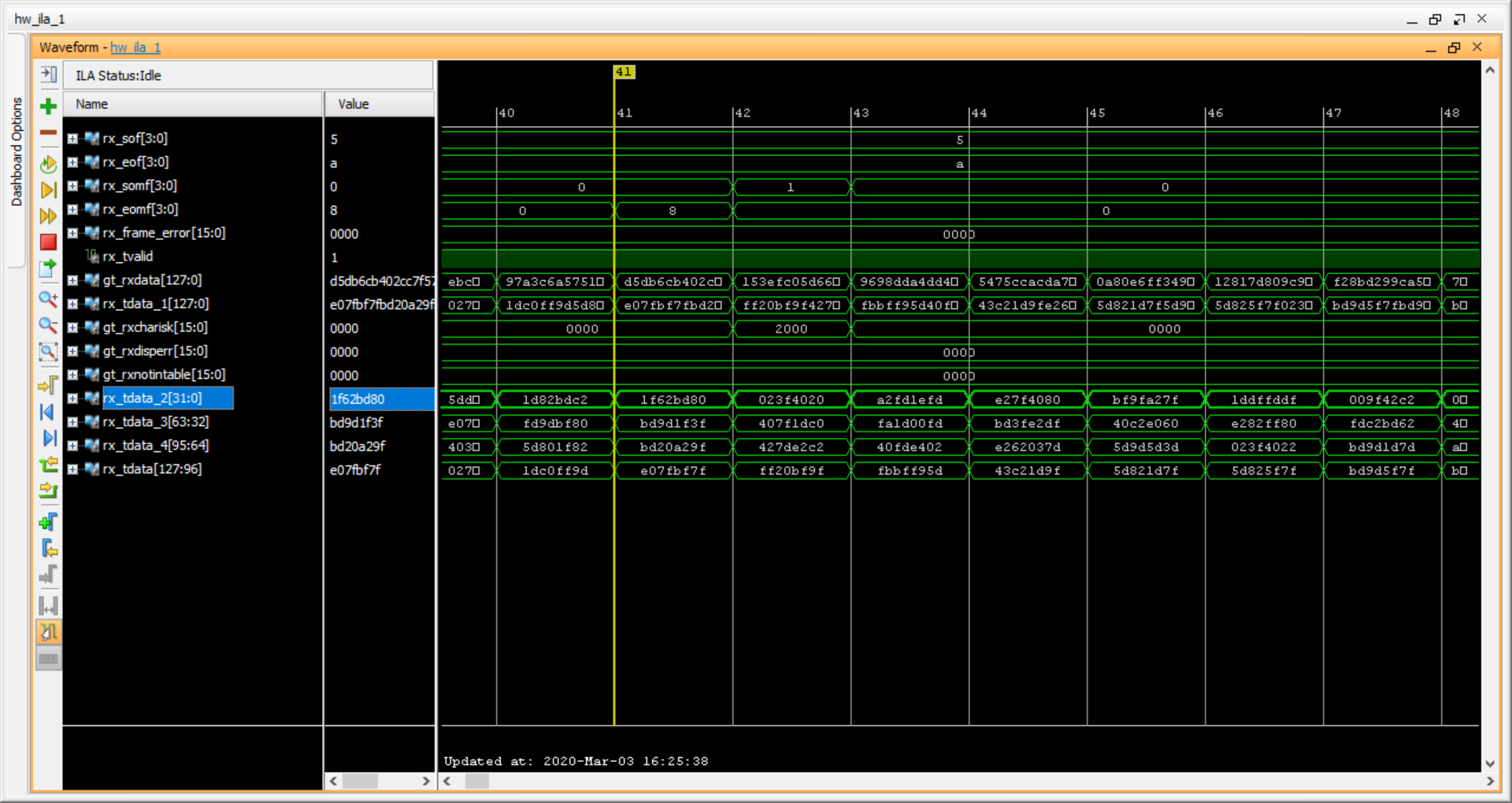

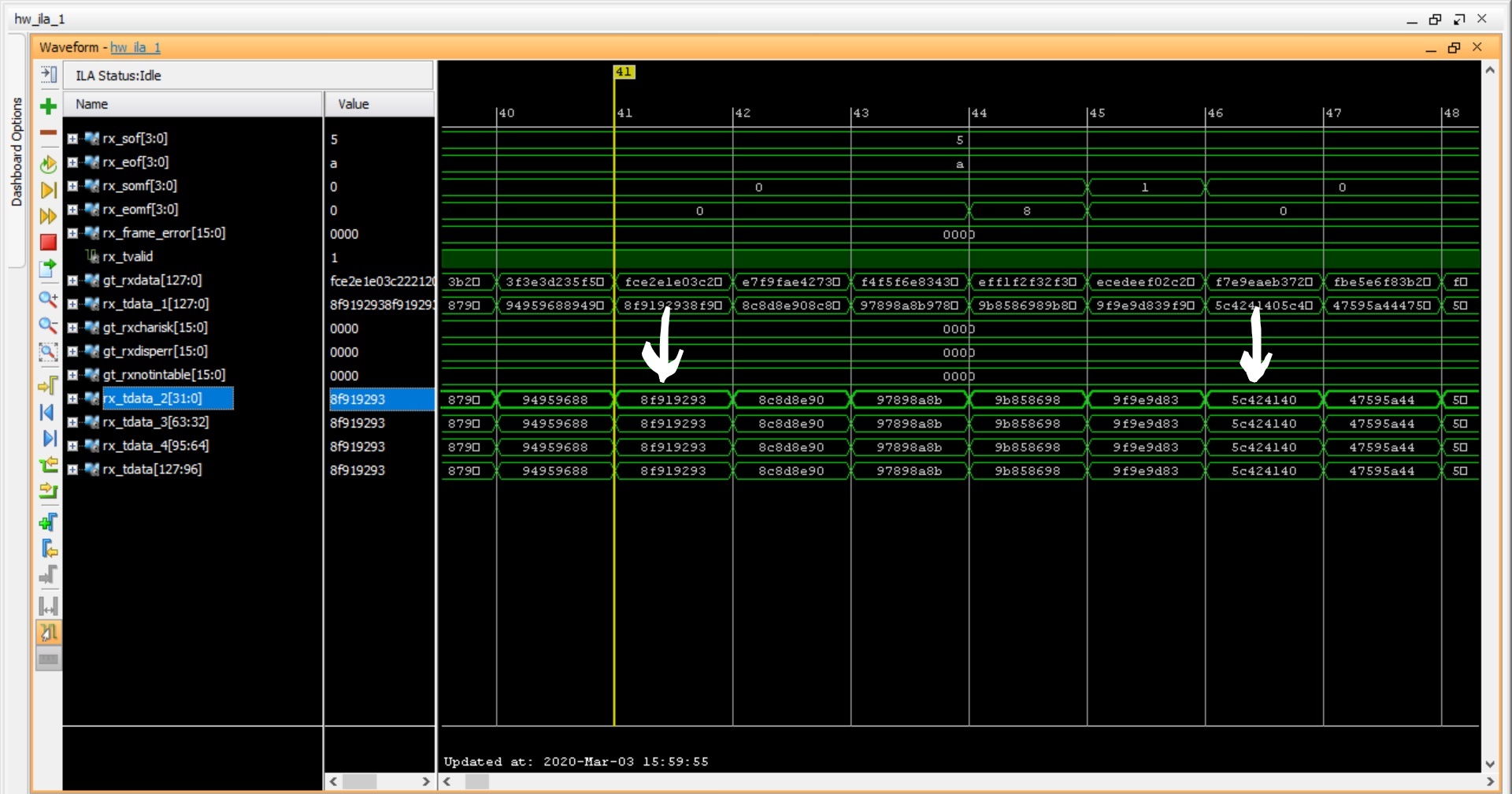

(2) Normal mode – a sine wave from the function generator is sampled by the ADC.

The data we collect after the transport layer mapping is incorrect. However, the results of signal RX_start_of_frame, RX_end_of_frame, RX_start_of_multiframe, RX_end_of_multiframe comply with the simulation results from the JESD204 example design.

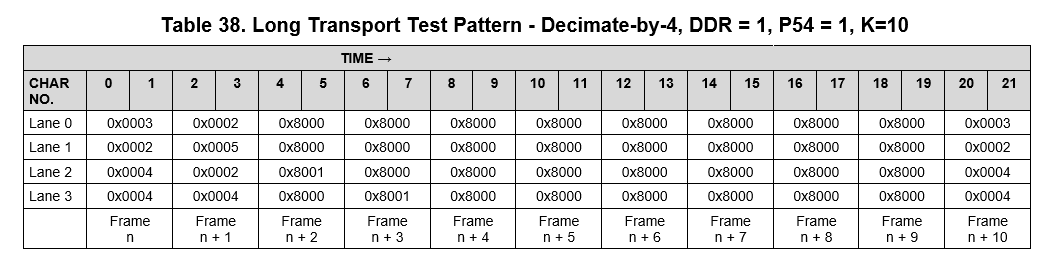

I think the JESD204 IP core is operating in the right way, so my guess about the cause of the error is I didn't correctly map the rx_data[127:0], here's what I did based on the output data format of the ADC:

//lane 0

signal0_sampl1 <= rx_tdata[31:17]; //data bits of every second sample on lane0

signal0_cntrl1 <= rx_tdata[16]; //control bit of every second sample on lane0

signal0_sampl0 <= rx_tdata[15:1]; //data bits of every first sample on lane0

signal0_cntrl0 <= rx_tdata[0]; //control bit of every first sample on lane0

//lane 1

signal1_sampl1 <= rx_tdata[63:49]; //data bits of every second sample on lane1

signal1_cntrl1 <= rx_tdata[48]; //control bit of every second sample on lane1

signal1_sampl0 <= rx_tdata[47:33]; //data bits of every first sample on lane1

signal1_cntrl0 <= rx_tdata[32]; //control bit of every first sample on lane1

//lane 2

signal2_sampl1 <= rx_tdata[95:81]; //data bits of every second sample on lane2

signal2_cntrl1 <= rx_tdata[80]; //control bit of every second sample on lane2

signal2_sampl0 <= rx_tdata[79:65]; //data bits of every first sample on lane2

signal2_cntrl0 <= rx_tdata[64]; //control bit of every first sample on lane2

//lane 3

signal3_sampl1 <= rx_tdata[127:113]; //data bits of every second sample on lane3

signal3_cntrl1 <= rx_tdata[112]; //control bit of every second sample on lane3

signal3_sampl0 <= rx_tdata[111:97]; //data bits of every first sample on lane3

signal3_cntrl0 <= rx_tdata[96]; //control bit of every first sample on lane3

Any help with the configuration and/or how I have to use my IQ samples from rx_data to get the original data of Ramp or Sinewave would be great.

Thanks in advance.

Best,

Haotian