Hi,

I use an ADC12DJ5200RF on a board I designed.

A 5200 MHz clock and a 32.5 MHz SYSREF are fed into the ADC, which operates with single-channel 10.4 G sampling.

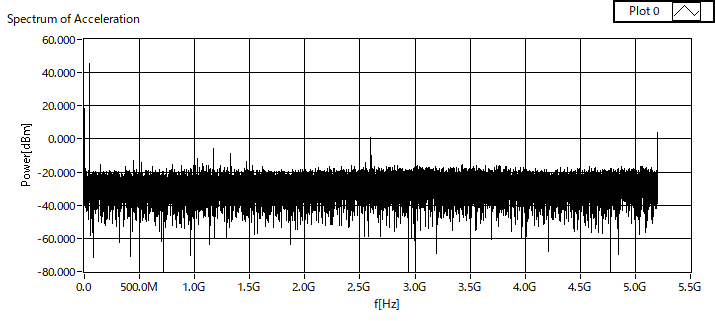

It seems like the output data has a 2.6 GHz noise component that should not be present. Is there a calibration method to reduce this?

The current settings and waveform FFT results are attached below.

Address(Hex) Set

0x0 0xb0

0x02b 0x15

0x2a2 0x30

0x200 0x00

0x61 0x00

0x201 0x01

0x202 0x03

0x204 0x03

0x48 0x03

0x360 0x10

0x361 0x10

0x362 0x10

0x363 0x10

0x364 0x10

0x365 0x10

0x366 0x10

0x367 0x10

0x29 0x20

0x29 0x70

0x30 0x00

0x31 0x20

0x32 0x00

0x33 0x20

0x60 0x01

0x61 0x00

0x62 0x05

0x61 0x01

0x200 0x01

0x2b0 0x01

0x6c 0x00

0x6c 0x01