|

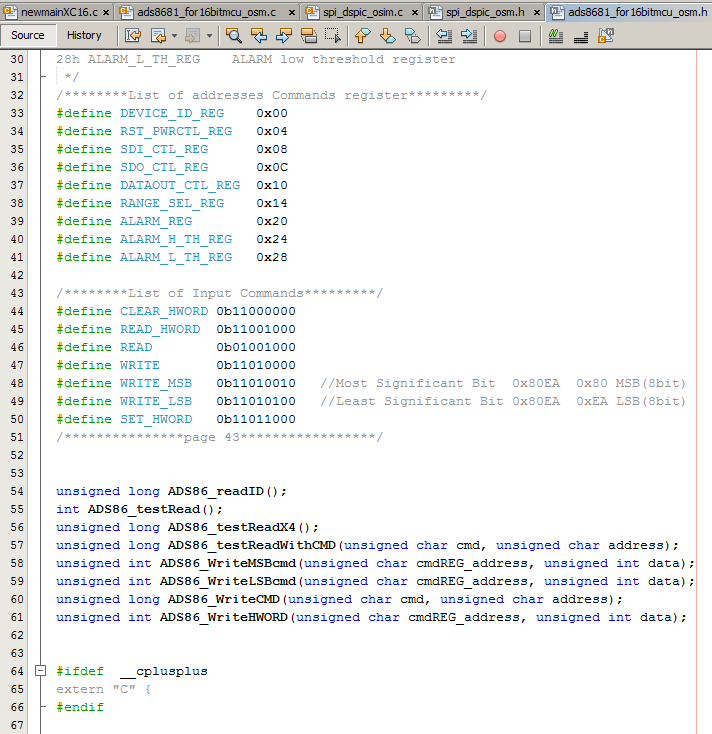

Sl. No. |

Functions |

Access Type |

Value in Hex |

Description |

|

1 |

Reset Pwr Cntrl Register |

Write |

0XD005 0069h

0xD204 0000h 0xD404 6930h |

First, write 0x69 to Address 0x05 (‘0’ is added at MSB to form 9 bit address)

Reset Register – MSB Data Reset Register – LSB Data |

|

2 |

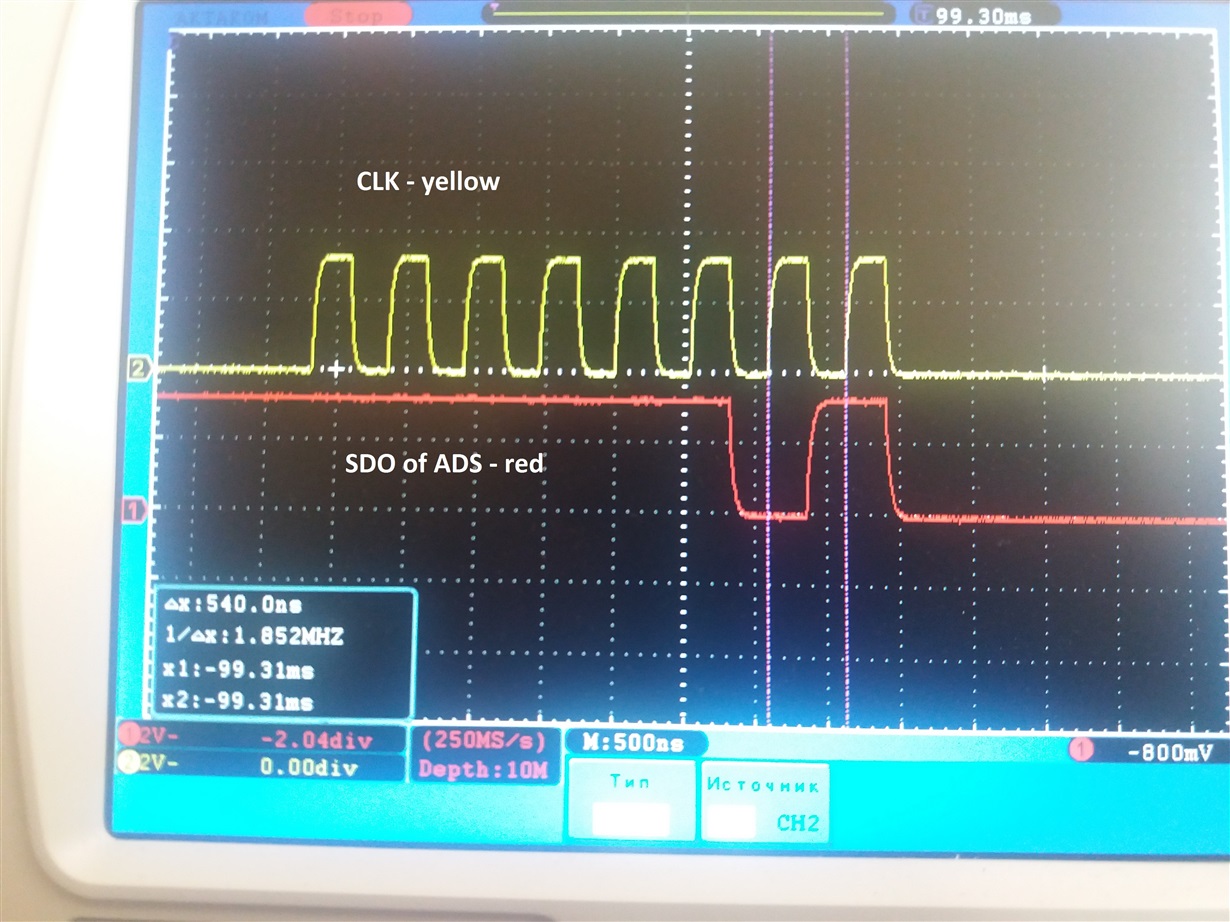

SDI Control Register |

Write |

0XD208 0000h

0XD408 0000h |

MSB Data

LSB Data – SPI with CPOL=0 & CPHASE=0 (device to Tx data on Rising Edge and Rx Data on Falling edge of SCLK) |

|

3 |

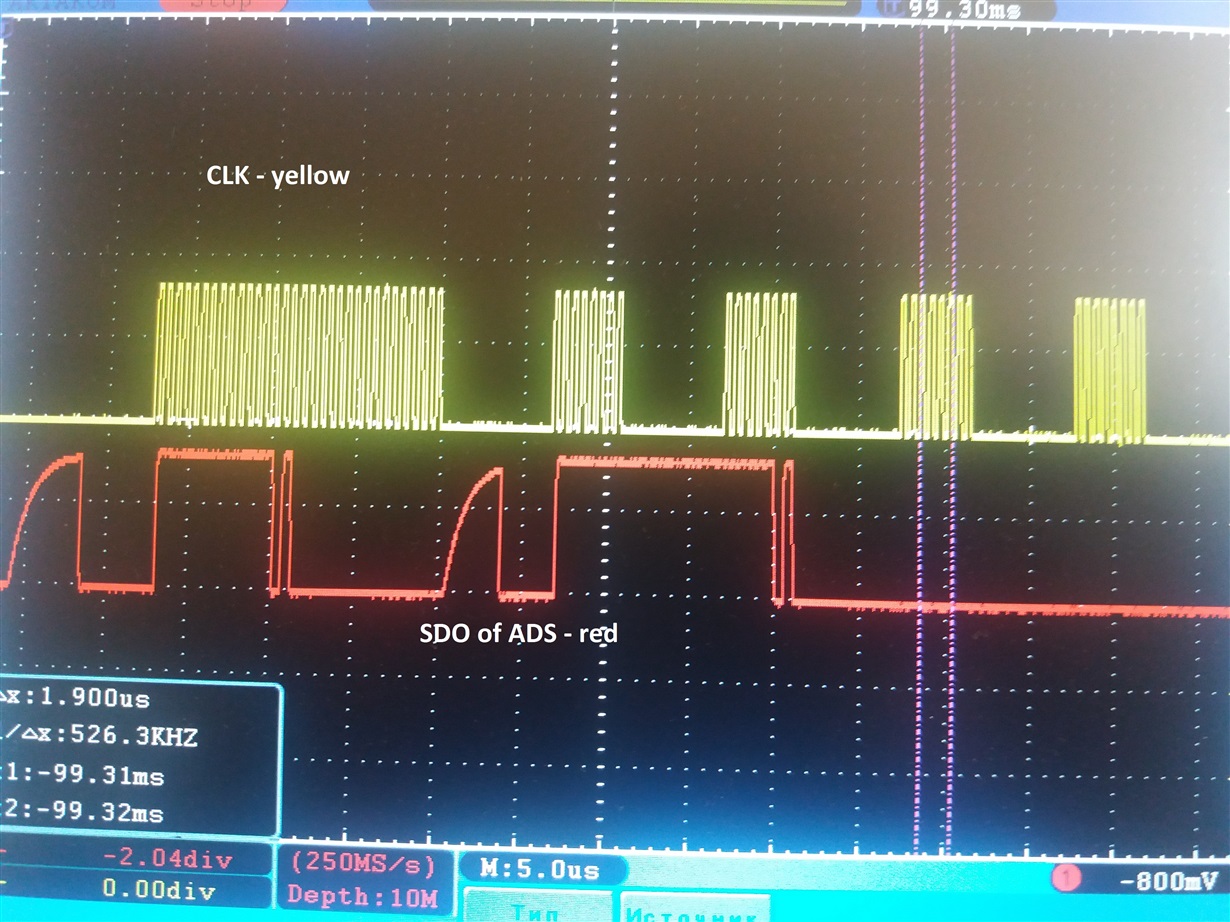

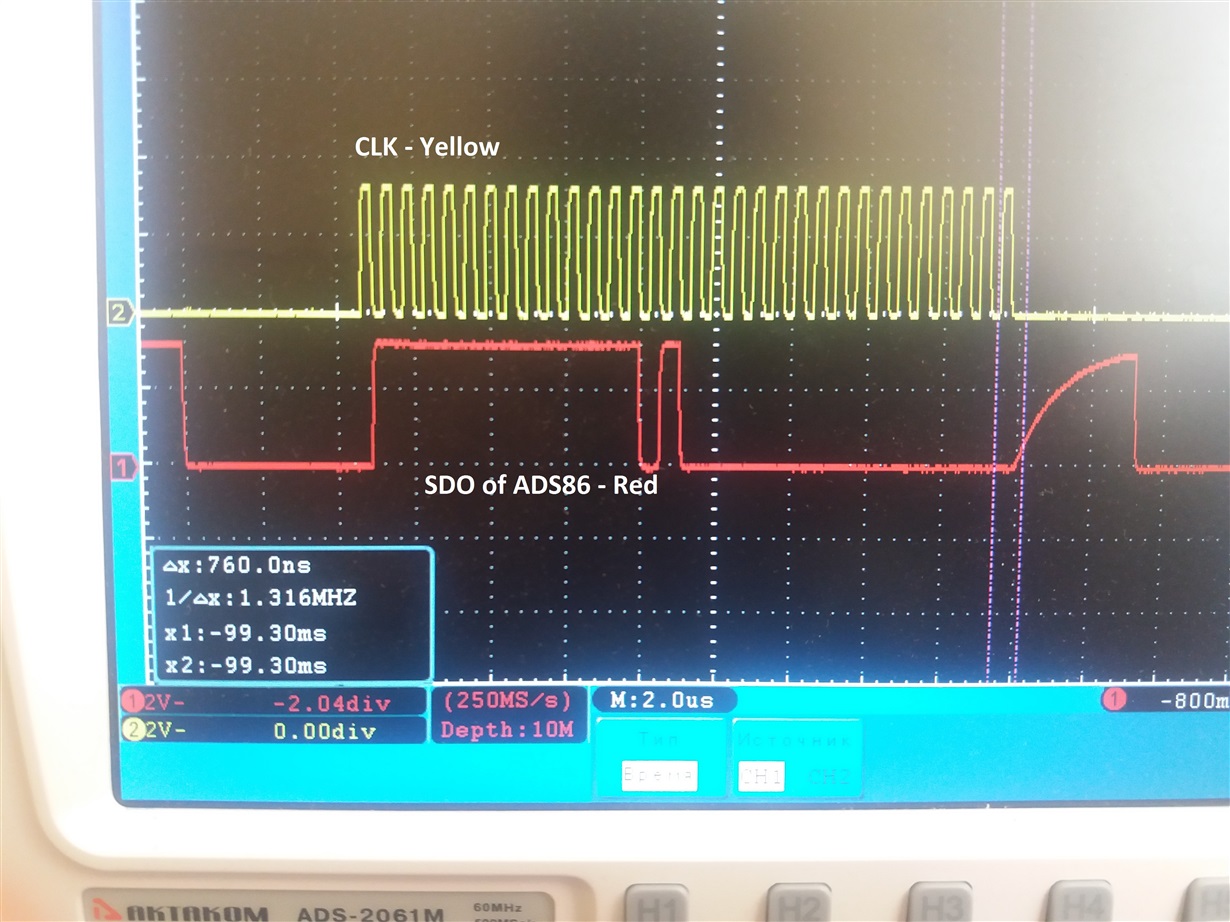

SDO Control Register |

Write |

0XD20C 0000h

0XD40C 0000h |

MSB Data

LSB Data – Internal Clock, SPI protocol same as SDI |

|

4 |

Range Select Register |

Write |

0XD214 0000h

0XD414 0001h |

MSB Data

LSB Data – Internal Ref Enabled, ±10.24V |

|

5 |

Output Data Control Register |

Write |

0XD210 0000h

0XD410 0000h |

MSB Data

LSB Data – ALARM not included, SDO data does not include Register Address |

|

6 |

NOP |

Write |

0x0000 0000h |

No operation |

Poornalatha K