Hello,

TLC2558 datasheet specify from SCLK rising edge to SDO valid, td(CLK-DOV), when FS=1.

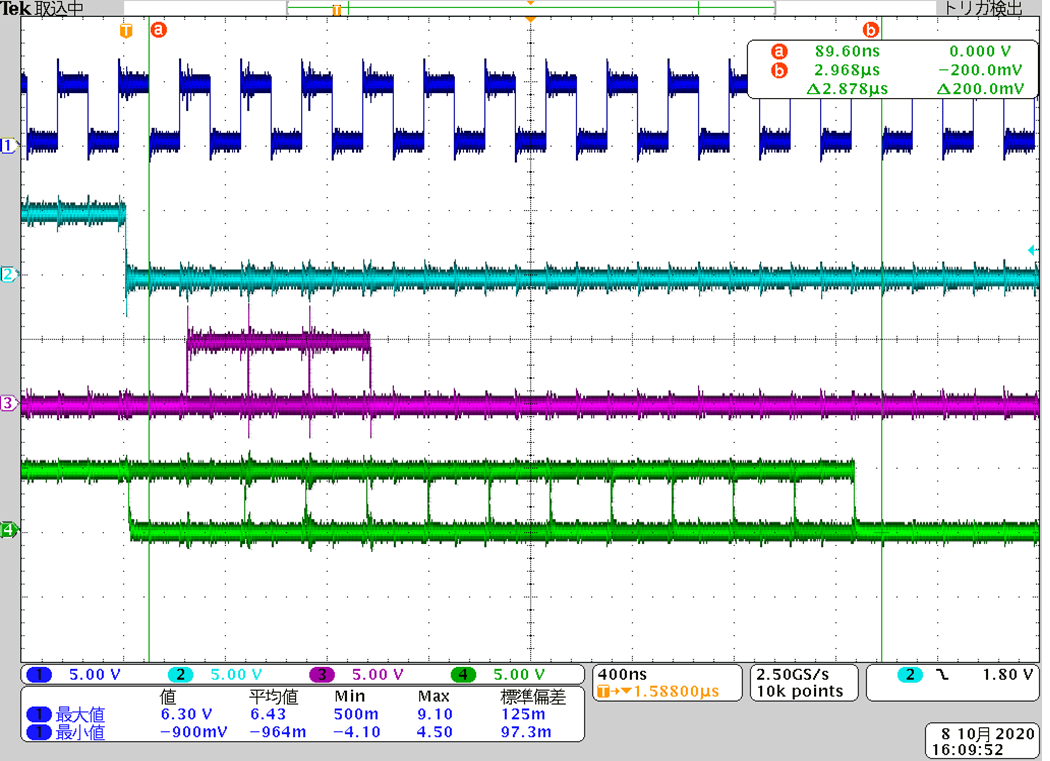

However, my customer captured SPI waveform when FS=1 as follows. (Ch1=SCLK, Ch2=CS, Ch3=SDI, Ch4=SDO)

It appears that SDO get valid at SCLK falling edge, not rising edge specified in the datasheet.

Is the datasheet wrong?

Best regards,

K.Hirano