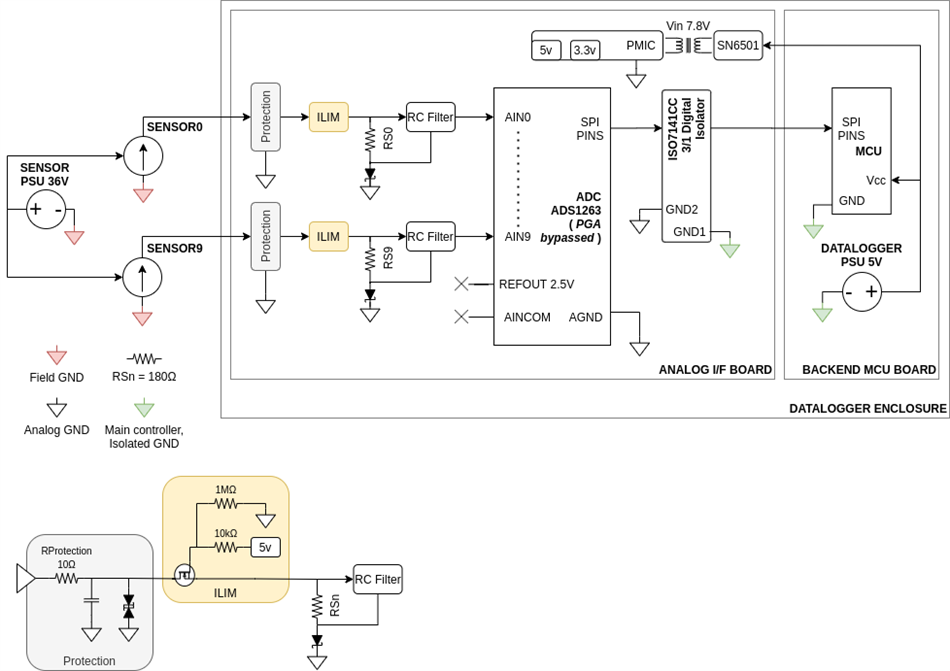

Hello, my name is Bontor from Tritronik, Indonesia. We are designing an IoT device (datalogger) that needs to read 10x sensors with 4-20mA output. Since all sensors and datalogger will be installed in a noisy outdoor environment, we need to take safety precaution in this design. We feel ADS1263 is suitable for this application since it has sufficient number of channels, sampling rate, and especially with TIDUC03 - "4- to 20-mA Analog Input Module Reference Design for Safety Applications" recommending such ADC chip for 4..20mA application.

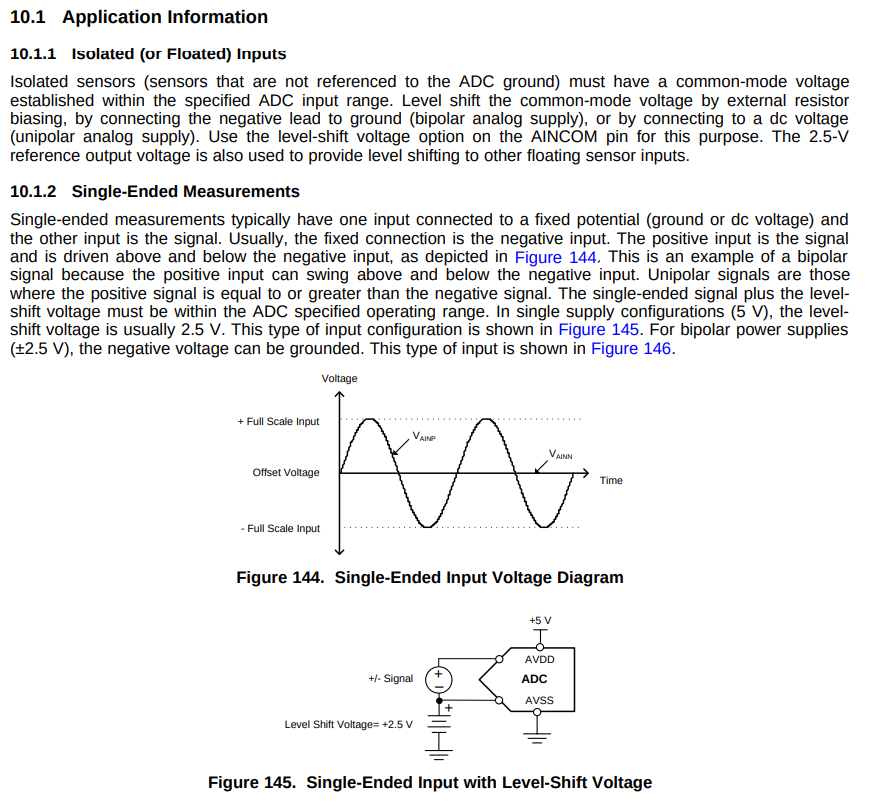

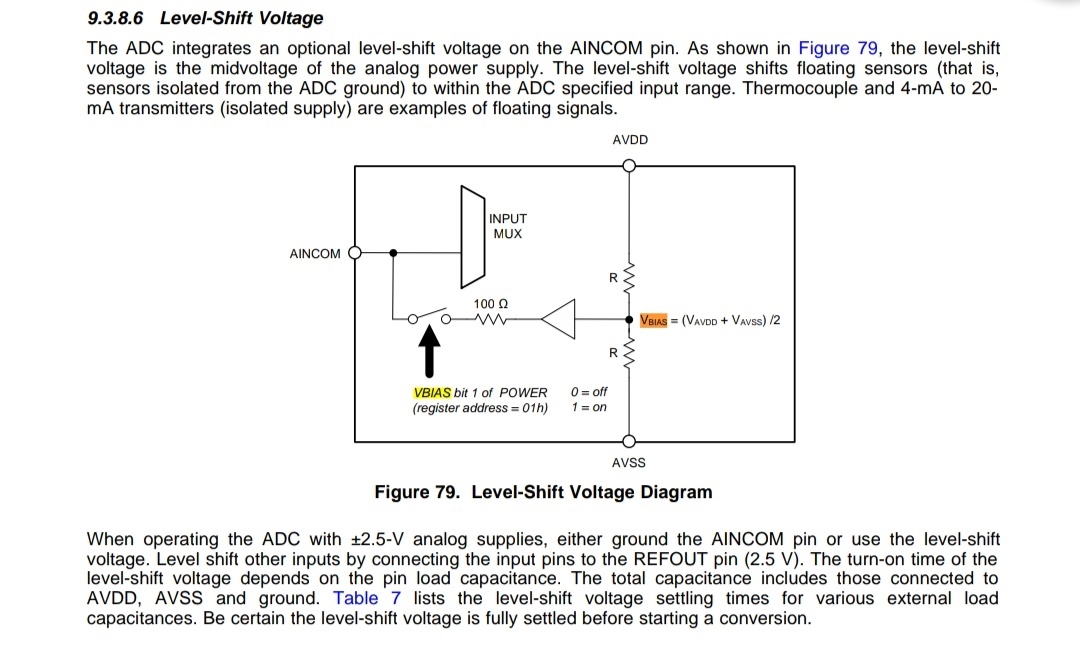

While we can use design references in TIDUC03 document, it doesnt show how to design a circuit for floating / single channel 4..20 mA application. Nor we find such design in ADS1263 datasheet. Closest we can get is as shown below from ADS1263 datasheet page 107

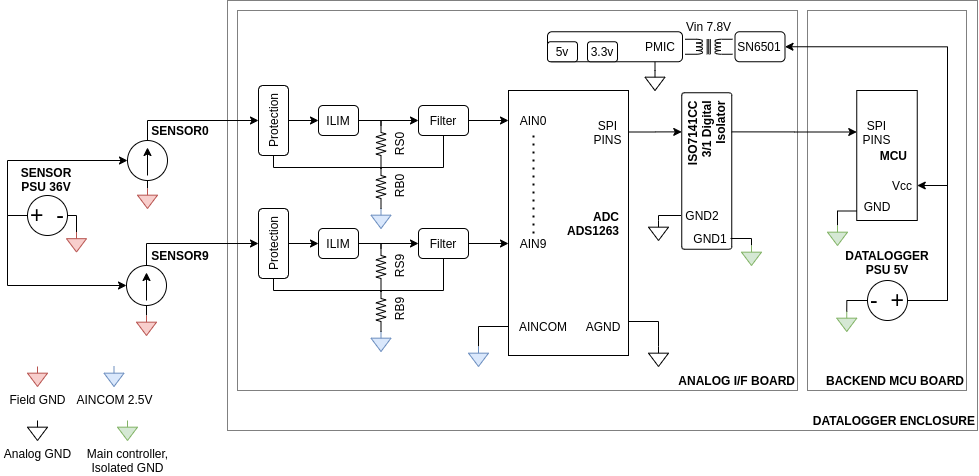

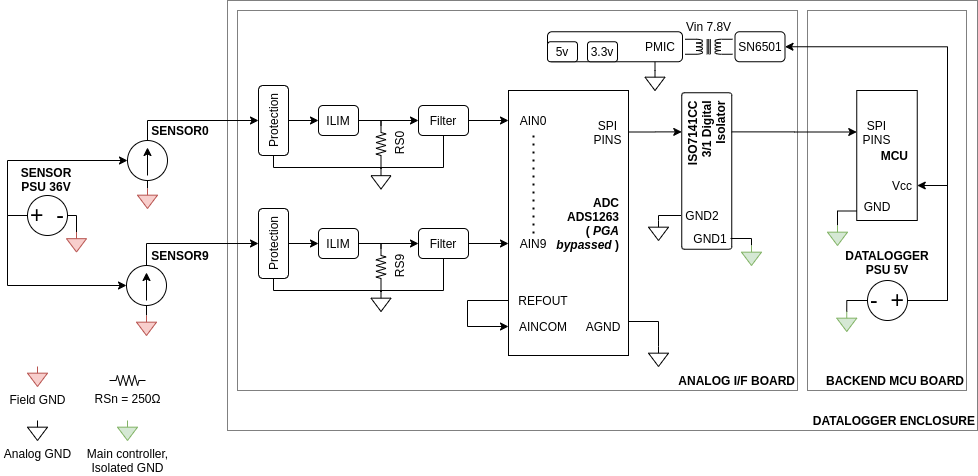

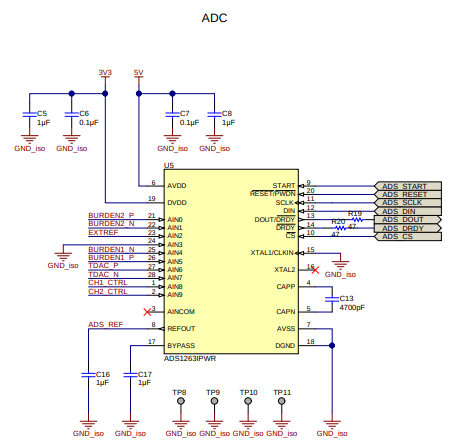

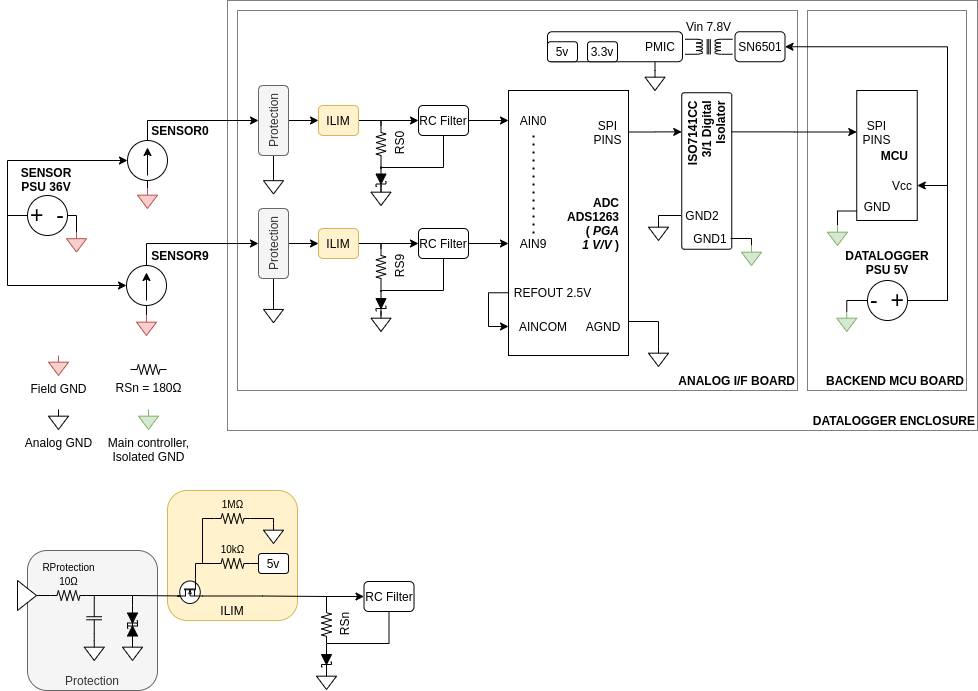

Based on TIDUC03 and Application Information above, we conclude that to use ADS1263 to measure floating input 4..20 mA in a single channel, we need to add external resistor to bias the +/- signal. Which means that the burden resistor, protection circuit (TVS diode), and analog filter in the analog front end should be connected to the bias resistor. We come up with high level design below, where RB0 will bias input signal to the ADS1263

My questions are:

- Is my design above, especially the way i interpret "biasing resistor", correct?

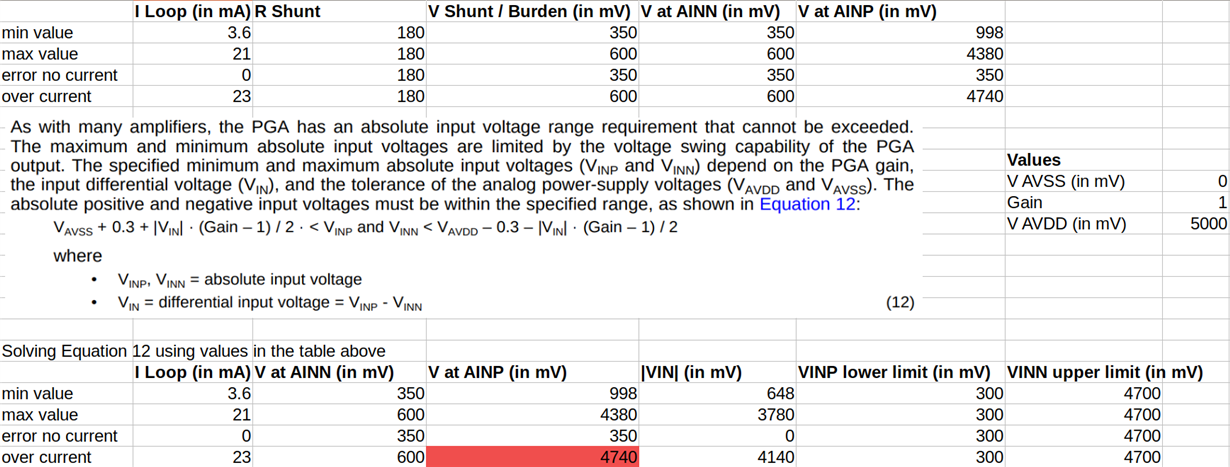

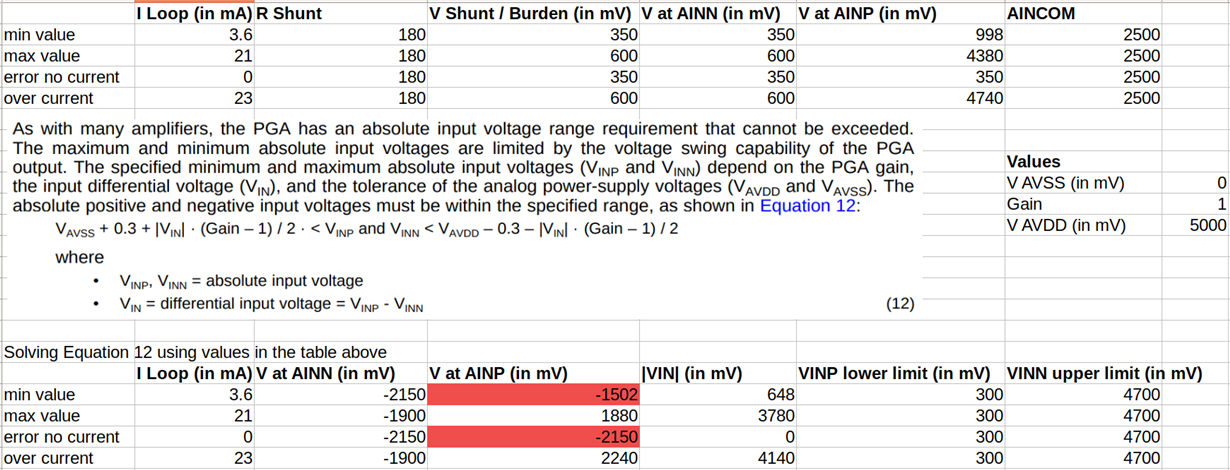

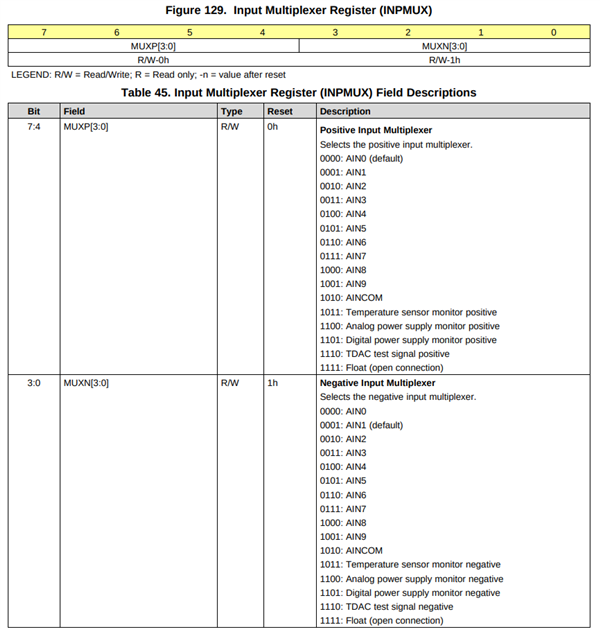

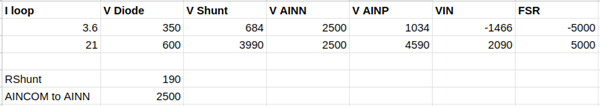

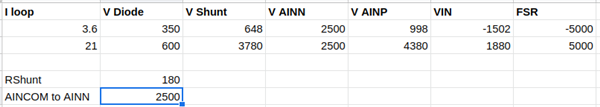

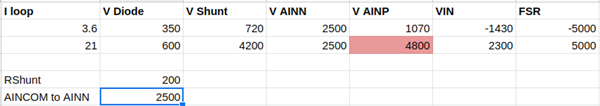

- To determine the value for biasing resistor (RBx), i will need to calculate the range of input signal, and ensure that the input signal is within ADC Input Voltage Spec → as mentioned in ADS1263 datasheet pg 116 "The next step in the design is determining the value of the RBIAS resistor, in order to level shift the RTD voltage to meet the ADC absolute input-voltage specification"

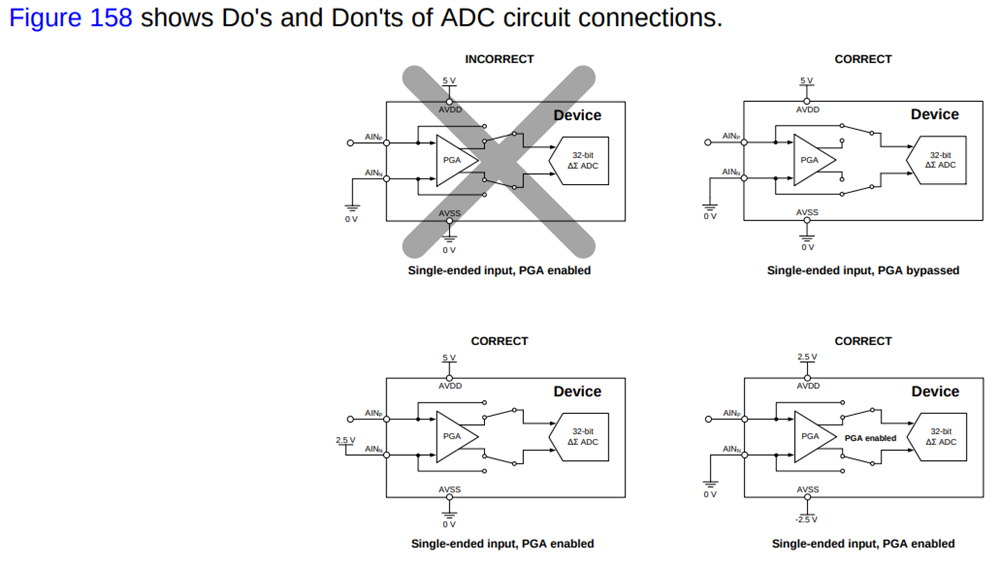

- Finally, regarding PGA, TIDUC03 recommends to use PGA 1/1 in order to increase input impedance. However, the way I understand it, ADS1263 datasheet page 119 does not specifically explains DO's and DONT's on using PGA for floating input circuit. Can I configure PGA 1/1 with my design above?

Thank you for taking your time reading this post.

BR,

Bontor

www.tritronik.com