Hi Team,

Would you let me know which SPI mode can support? (In Master side)

In my understand only MODE0 support, but please let me know other mode can support or not.

Thank you.

Best Regards,

Jade

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Team,

Would you let me know which SPI mode can support? (In Master side)

In my understand only MODE0 support, but please let me know other mode can support or not.

Thank you.

Best Regards,

Jade

Jade,

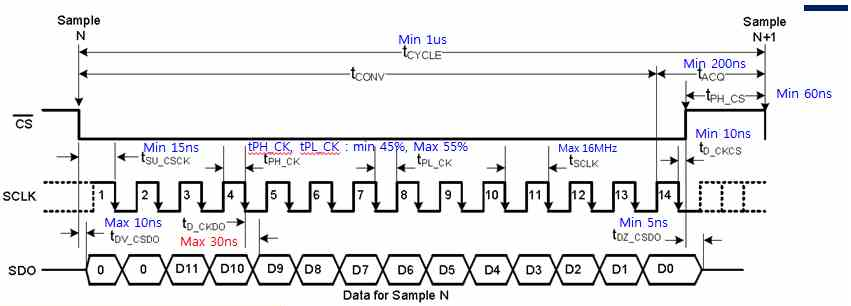

In typical operating conditions, since the data on DOUT changes on the falling edge and is captured on the next rising edge, this can be considered Mode 0 operation for the host. But this need not always be the case.

Consider a scenario where the ADS7042 is operated at the max SCLK of 16MHz (62.5ns clock period) and with the lower AVDD range of 1.65V to 1.8V. As per the timing characteristics in Section 8.6 of the datasheet, the SCLK falling to DOUT valid delay can be as much as 50ns. And buffers and large trace capacitances can delay this signal further. In such cases, it will be required to operate the host in Mode 1 and capture the data on the next falling edge of SCLK.

So the choice of SPI mode for the host is dependent on the operating conditions of your particular design.

Regards,

Sandeep

Hi Sandeep,

Customer use AVDD=3.3V. In this case, support MODE 0 only?

1. Data change at falling edge, would you let me know minimum data hold timing from falling edge? tD_CKDO is maximum delay for change data.

Would you let me know minimum tHOLD spec?

2. From falling edge, if customer satisfy enough hold time that requested by MASTER, it looks like support all MODE0~3, right?

FYI, their MASTER Setting are below:

IPQ8069 Master Setting

- SPI Clock 8MHz

- Access Interval : min 300ns

- Supported SPI Mode #1 : Mode 0

.Clock Polarity(CPOL): 0

.Clock Phase(CPHA) : 0

=> Master MISO: captured at rising edge

- Supported SPI Mode #2 : Mode 3

.Clock Polarity(CPOL): 1

.Clock Phase(CPHA) : 1

=> Master MISO: captured at rising edge

- Supported SPI Mode #3 : Mode 1

.Clock Polarity(CPOL): 0

.Clock Phase(CPHA) : 1

=> Master MISO: captured at falling edge

(guarantee Hold time : CAD routing Delay + min tD_CKDO[Unkown])

- Supported SPI Mode #4 : Mode 2

.Clock Polarity(CPOL): 1

.Clock Phase(CPHA) : 0

=> Master MISO: captured at falling edge

(guarantee Hold time : CAD routing Delay + min tD_CKDO[Unkown])

Thank you.

Best Regards,

Jade