Hi Team,

I heard my customer's system requires sampling frequency(fs) = 8kHz and audio data bit=16bit (mono).

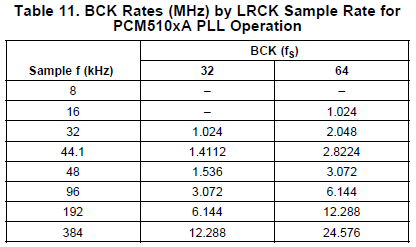

Should I consider PCM5100A doesn't support the requirement with 3-Wire PCM from Table 11?

I would like to ask if PCM5100A supports the requirement with 4Wire-I2S.

Best Regards,

Yaita / Japan disty

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.